現在、私たちが日常生活で使用している電気・電子機器はすべて、半導体デバイスの製造工程を利用して製造された集積回路で構成されています。ザ・ 電子回路 のような純粋な半導体材料で作られたウェーハ上に作成されます シリコンおよびその他の半導体 フォトリソグラフィーと化学プロセスを含む複数のステップを持つ化合物。

半導体製造のプロセスは、1960年代初頭にテキサスから始まり、その後世界中に広がりました。

BiCMOSテクノロジー

これは主要な半導体技術の1つであり、高度に開発された技術であり、1990年代には、バイポーラ接合トランジスタとCMOSという2つの別個の技術が組み込まれています。 トランジスタ 単一の最新の集積回路で。したがって、このテクノロジーをより快適に利用するために、CMOSテクノロジーとバイポーラテクノロジーを簡単に見ることができます。

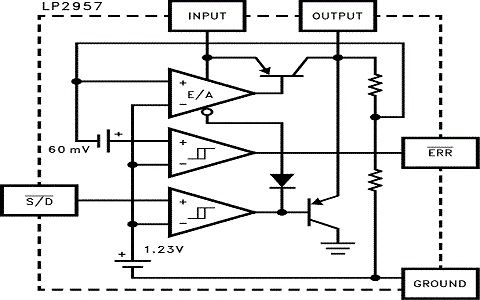

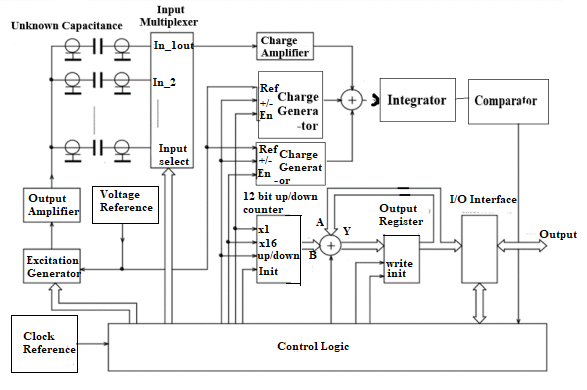

BiCMOS CME8000

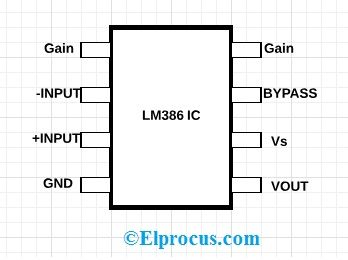

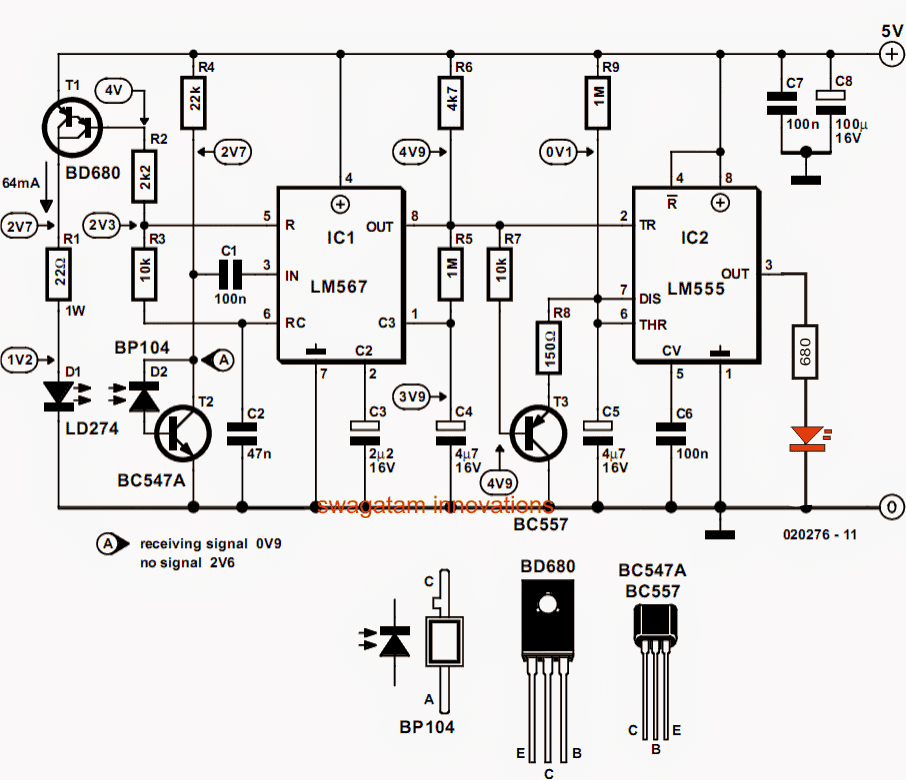

示されている図は最初のものです アナログ/デジタル レシーバICであり、非常に高感度のBiCMOS集積レシーバです。

CMOSテクノロジー

これは、電子計算機の製造元として開始されたMOSテクノロジーまたはCSG(Commodore Semiconductor Group)を補完するものです。その後、CMOS技術と呼ばれるMOS技術の補完物がデジタルなどの集積回路の開発に使用されます 論理回路 に加えて マイクロコントローラー sおよびマイクロプロセッサ。 CMOSテクノロジは、高いパッキング密度で消費電力が少なく、ノイズマージンが低いという利点があります。

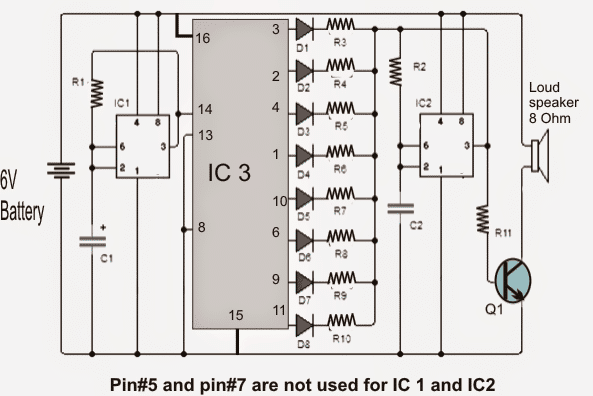

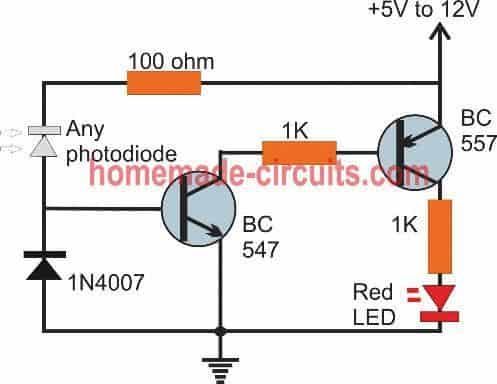

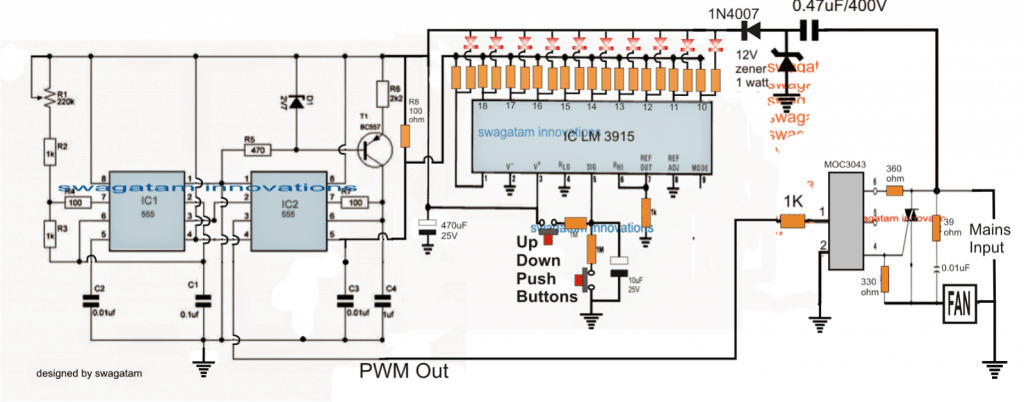

CMOS CD74HC4067

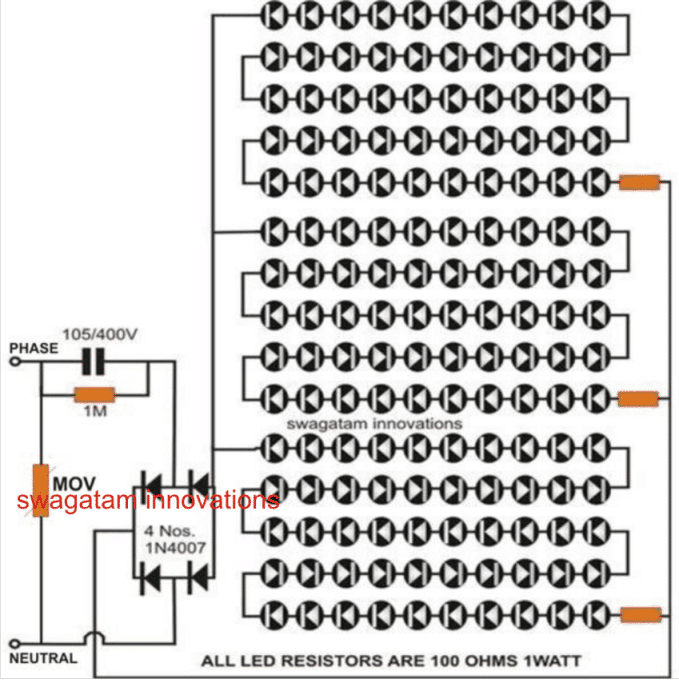

この図は、デジタル制御スイッチデバイスの製造におけるCMOSテクノロジの利用を示しています。

バイポーラテクノロジー

バイポーラトランジスタは集積回路の一部であり、その動作は2種類の半導体材料に基づいているか、両方の種類の電荷キャリア正孔と電子に依存しています。これらは一般に次の2種類に分類されます。 PNPとNPN 、その3つの端子のドーピングとそれらの極性に基づいて分類されます。高いスイッチング速度と優れたノイズ性能を備えた入出力速度を提供します。

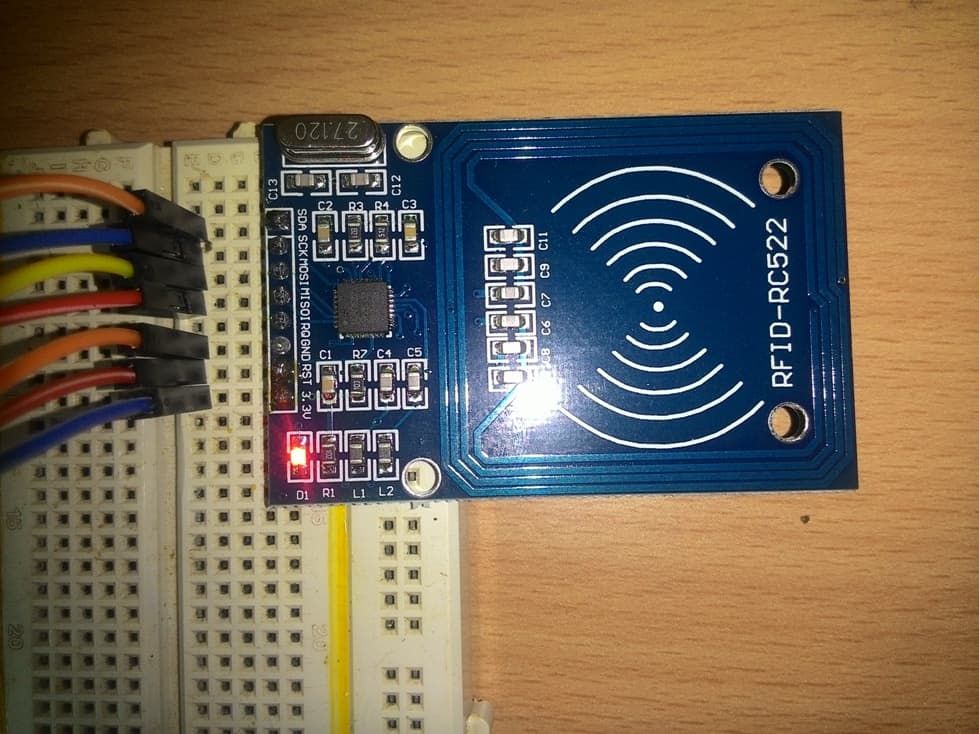

バイポーラAM2901CPC

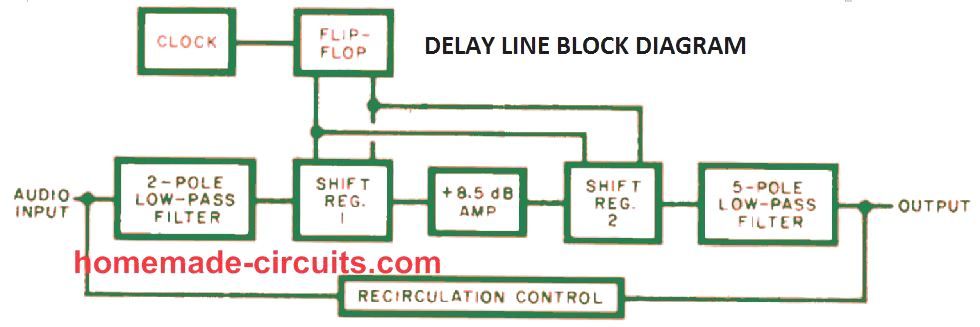

この図は、RISCプロセッサAM2901CPCでのバイポーラテクノロジの利用を示しています。

BiCMOSロジック

これは、NMOS技術とPMOS技術を融合させた複雑な処理技術であり、非常に低消費電力のバイポーラ技術とCMOS技術よりも高速であるという利点があります。MOSFETは高入力インピーダンスの論理ゲートを付与し、バイポーラトランジスタは高電流ゲインを提供します。

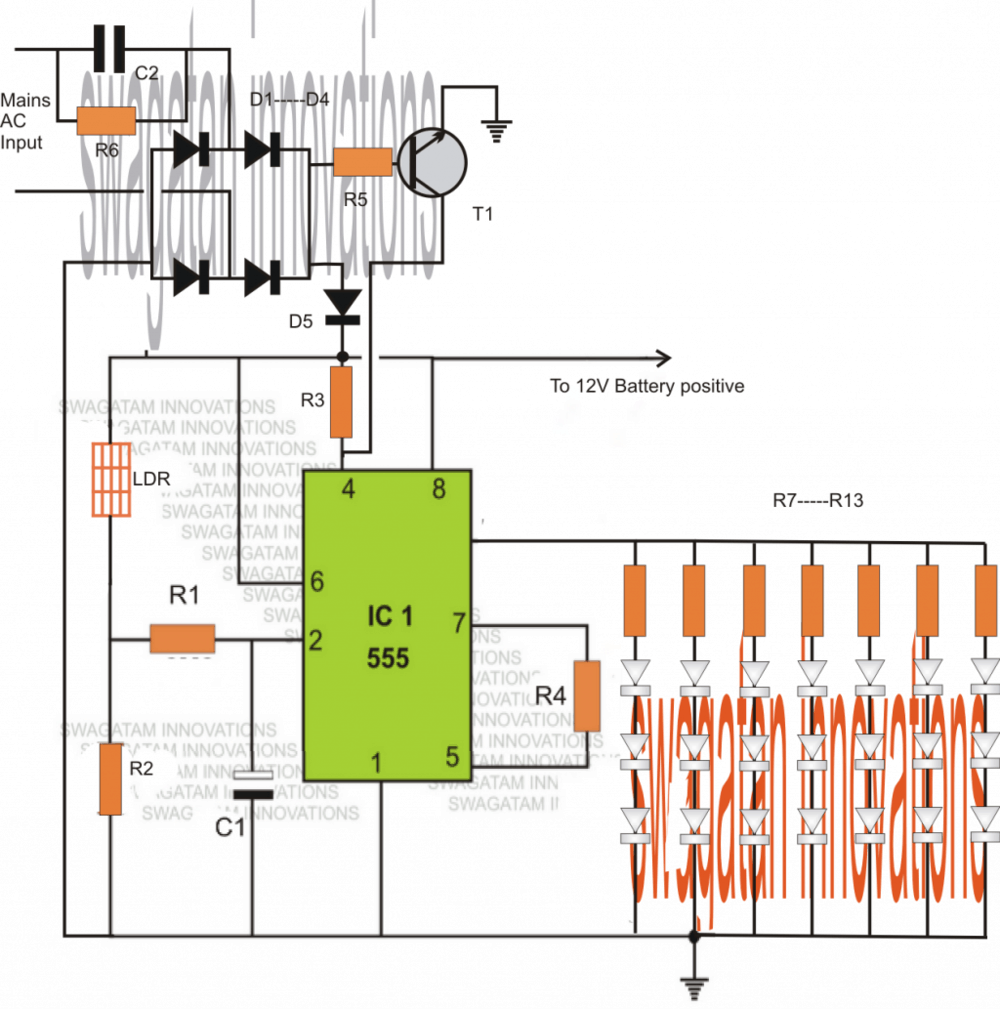

BiCMOS製造の14のステップ

BiCMOSの製造は、BJTとCMOSの製造プロセスを組み合わせたものですが、単なるバリエーションがベースの実現です。次の手順は、BiCMOSの製造プロセスを示しています。

ステップ1: 下図のようにP基板を取ります

P基板

ステップ2: p基板は酸化物層で覆われています

酸化物層を備えたP基板

ステップ3: 酸化物層に小さな開口部が作られています

酸化物層に開口部を作る

ステップ4: N型不純物は開口部から高濃度にドープされています

N型不純物は開口部から高濃度にドープされています

ステップ5: P –エピタキシー層は表面全体に成長します

エピタキシー層は表面全体に成長します

ステップ6 :この場合も、層全体が酸化物層で覆われ、この酸化物層に2つの開口部が作られます。

“UPSシステムの仕組み ”

酸化物層に2つの開口部が作られています

ステップ7 :酸化物層を介して作られた開口部から、n型不純物が拡散してnウェルを形成します

n型不純物が拡散してnウェルを形成

ステップ8: 酸化物層を介して3つの開口部が作成され、3つのアクティブデバイスが形成されます。

酸化物層に3つの開口部を作り、3つのアクティブデバイスを形成します

ステップ9: MOSFETとPMOSのゲート端子は、ThinoxとPolysiliconで表面全体を覆ってパターン化することによって形成されます。

MOSFETとPMOSのゲート端子はThinoxとPolysiliconで形成されています

ステップ10: P不純物を添加してBJTのベース端子を形成し、同様のN型不純物を高濃度にドープしてBJTのエミッタ端子、NMOSのソースとドレインを形成し、接触のためにN型不純物をNウェルにドープします。コレクタ。

BJTのベース端子を形成するためにP不純物が追加されます

ステップ11: PBSのソース領域とドレイン領域を形成し、Pベース領域で接触させるために、P型不純物が高濃度にドープされています。

P型不純物は高濃度にドープされてPMOSのソース領域とドレイン領域を形成します

ステップ12: 次に、表面全体が厚い酸化物層で覆われます。

表面全体が厚い酸化物層で覆われている

ステップ13: 厚い酸化物層を通して、カットは金属接点を形成するようにパターン化されます。

カットは、金属接点を形成するようにパターン化されています

ステップ14 :金属接点は酸化物層に切り込みを入れて作られ、端子は下図のように命名されています。

金属接点はカットを通して作られ、端子には名前が付けられています

上図に、NMOS、PMOS、BJTを組み合わせたBICMOSの製造を示します。製造プロセスでは、チャネルストップインプラント、厚層酸化、ガードリングなどのいくつかの層が使用されます。

CMOSとバイポーラの両方の技術を含めると、製造は理論的に困難になります。寄生虫 バイポーラトランジスタ 不注意で生成されるのは、pウェルおよびnウェルCMOSの処理中の製造の問題です。 BiCMOSの製造では、バイポーラおよびCMOSコンポーネントの微調整のために多くの追加ステップが追加されました。したがって、総製造コストが増加します。

チャネルストッパーは、チャネル領域の広がりを制限するため、または寄生チャネルの形成を回避するために、注入または拡散または他の方法を使用することによって、上図に示すように半導体デバイスに埋め込まれる。

高インピーダンスノードがある場合、表面漏れ電流が発生する可能性があり、電流の流れが制限されている場所での電流の流れを回避するために、これらのガードリングが使用されます。

BiCMOSテクノロジーの利点

- アナログアンプの設計は、入力として高インピーダンスのCMOS回路を使用することで容易になり、改善され、残りはバイポーラトランジスタを使用することで実現されます。

- BiCMOSは本質的に温度とプロセスの変動に強く、電気的パラメータの変動が少なく、経済的な考慮事項(プライムユニットの割合が高い)を提供します。

- 高負荷電流のシンクとソーシングは、要件に応じてBiCMOSデバイスによって提供できます。

- バイポーラ技術とCMOS技術のグループであるため、速度が重要なパラメータである場合はBJTを使用でき、電力が重要なパラメータである場合はMOSを使用でき、サイクルタイムを短縮して大容量負荷を駆動できます。

- バイポーラ技術単独よりも消費電力が少ない。

- この技術は、アナログ電力管理回路やBiCMOSアンプなどのアンプ回路で頻繁に使用されています。

- 入力/出力を多用するアプリケーションに最適で、柔軟な入力/出力(TTL、CMOS、ECL)を提供します。

- これには、CMOSテクノロジのみと比較して速度パフォーマンスが向上するという利点があります。

- 脆弱性をキャッチアップします。

- 双方向機能があります(必要に応じてソースとドレインを交換できます)。

BiCMOSテクノロジーの欠点

- この技術の製造プロセスは、CMOS技術とバイポーラ技術の両方で構成されており、複雑さが増しています。

- 製造プロセスの複雑さが増すため、製造コストも増加します。

- デバイスが多いほど、リソグラフィは少なくなります。

BiCMOSテクノロジーとアプリケーション

- これは、高密度と速度のAND関数として分析できます。

- この技術は、市場に出回っている以前のバイポーラ、ECL、およびCMOSの代替として使用されています。

- 一部のアプリケーション(電力の予算が限られている)では、BiCMOSの速度性能はバイポーラの速度性能よりも優れています。

- このテクノロジーは、集中的な入出力アプリケーションに最適です。

- BiCMOSのアプリケーションは、当初、従来のCISCマイクロプロセッサではなくRISCマイクロプロセッサにありました。

- この技術は、主にメモリと入出力などのマイクロプロセッサの2つの領域でそのアプリケーションに優れています。

- アナログおよびデジタルシステムで多くのアプリケーションがあり、その結果、単一チップがアナログ-デジタル境界にまたがっています。

- それはギャップを越えて、行動方針と回路マージンを越えることを可能にします。

- 高インピーダンス入力を提供するため、サンプルおよびホールドアプリケーションに使用できます。

- これは、加算器、ミキサー、ADC、DACなどのアプリケーションでも使用されます。

- バイポーラとCMOSの限界を克服するために オペアンプ BiCMOSプロセスは、オペアンプの設計に使用されます。オペアンプでは、高ゲインと高周波特性が求められます。これらのBiCMOSアンプを使用することで、これらすべての望ましい特性を得ることができます。

この記事では、BiCMOSテクノロジとその製造、長所、短所、およびアプリケーションについて簡単に説明します。このテクノロジーについての理解を深めるために、以下のコメントとしてクエリを投稿してください。

写真クレジット:

- BiCMOS CME8000 by c-max-time

- CMOS CD74HC4067 by bdtic

- バイポーラAM2901CPC シリリウム