さまざまなタイプのデジタルシステムは、ANDゲート、NANDゲート、ORゲートなど、ごくわずかなタイプの基本的なネットワーク構成から構築されます。これらの基本回路は、さまざまなトポロジの組み合わせで何度も使用されます。デジタルシステムは、ロジックの実行に加えて、2進数も格納する必要があります。これらのメモリーセルの場合、 フリップ・フロップ' は設計されています。バイナリ加算などの一部の機能を実行します。したがって、そのような機能を実行するには、 論理ゲート およびFLIP-FLOPは、シングルチップIC上に設計されています。これらのICは、デジタルシステムの実用的な構成要素を形成します。バイナリ加算に使用されるそのようなビルディングブロックの1つは、キャリー先見加算器です。

キャリー先見加算器とは何ですか?

デジタルコンピュータには、加算、減算、乗算、除算などの算術演算を実行できる回路が含まれている必要があります。これらの中で、加算と減算は基本的な操作ですが、乗算と除算はそれぞれ繰り返しの加算と減算です。

これらの操作を実行するために、「加算回路」は基本的な論理ゲートを使用して実装されます。 加算回路 半加算器、全加算器、リップルキャリー加算器、およびキャリー先見加算器として進化しています。

これらのキャリー先見加算器の中には、より高速な加算器回路があります。より複雑なハードウェア回路を使用することにより、加算中に発生する伝搬遅延を低減します。これは、リップルキャリー加算器回路を変換して、加算器のキャリーロジックを2レベルロジックに変更することによって設計されています。

4ビットキャリー先見加算器

並列加算器では、各全加算器のキャリー出力は、次の高次状態へのキャリー入力として与えられます。したがって、これらの加算器は、キャリー入力がその状態で使用可能でない限り、どの状態のキャリーおよび合計出力も生成できません。

したがって、計算が行われるためには、回路はキャリービットがすべての状態に伝搬するまで待機する必要があります。これにより、回路にキャリー伝搬遅延が発生します。

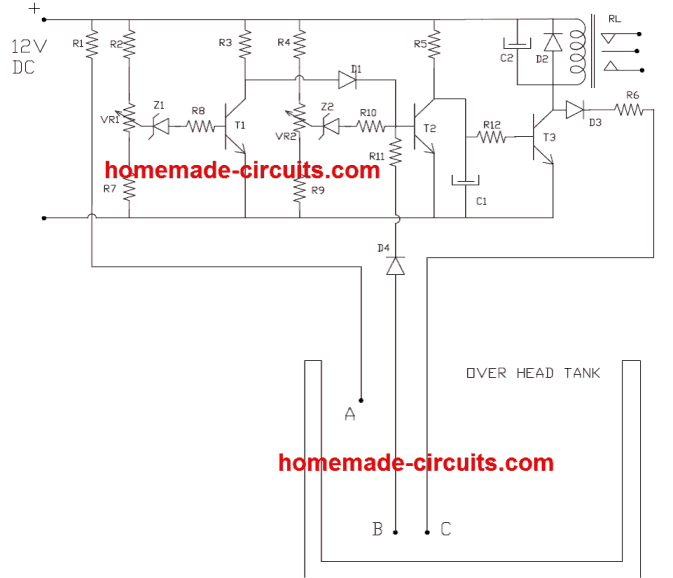

4ビット-リップル-キャリー-加算器

上記の4ビットリップルキャリー加算器回路について考えてみます。ここで、合計S3は、入力A3とB3が与えられるとすぐに生成できます。ただし、キャリービットC2が適用されるまで、キャリーC3は計算できませんが、C2はC1に依存します。したがって、最終的な定常状態の結果を生成するには、キャリーがすべての状態に伝播する必要があります。これにより、回路のキャリー伝搬遅延が増加します。

加算器の伝搬遅延は、「各ゲートの伝搬遅延に回路のステージ数を掛けたもの」として計算されます。多数のビットを計算するには、ステージを追加する必要があり、遅延がさらに悪化します。したがって、この状況を解決するために、キャリー先見加算器が導入されました。

キャリー先見加算器の機能を理解するために、4ビットのキャリー先見加算器について以下に説明します。

4ビット-キャリー-先見-加算器-ロジック-図

この加算器では、加算器の任意のステージでのキャリー入力は、独立したステージで生成されたキャリービットから独立しています。ここで、任意のステージの出力は、前のステージで追加されたビットと、最初のステージで提供されたキャリー入力にのみ依存します。したがって、どのステージの回路も前のステージからのキャリービットの生成を待つ必要はなく、キャリービットはいつでも評価できます。

キャリー先見加算器の真理値表

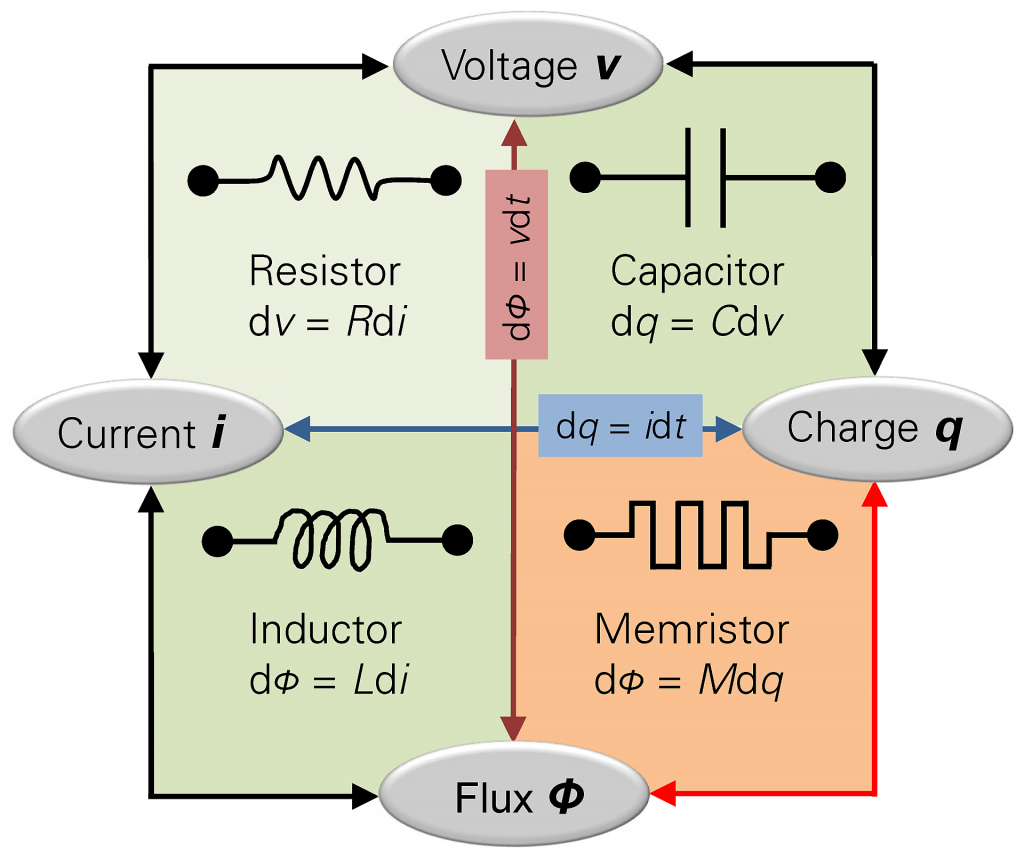

この加算器の真理値表を導出するために、2つの新しい用語が導入されました-キャリー生成とキャリー伝播。キャリーCi + 1が生成されるたびに、キャリーはGi = 1を生成します。 AiとBiの入力に依存します。 AiとBiの両方が1の場合、Giは1です。したがって、GiはGi = Aiとして計算されます。 Bi。

キャリー伝搬されたPiは、CiからCi +1へのキャリーの伝搬に関連付けられています。 Pi =Ai⊕Biとして計算されます。この加算器の真理値表は、全加算器の真理値表を変更することで導出できます。

GiとPiの用語を使用すると、SumSiとCarryCi + 1は次のようになります–

- Si =Pi⊕Gi。

- Ci + 1 = Ci.Pi + Gi。

したがって、キャリービットC1、C2、C3、およびC4は次のように計算できます。

- C1 = C0.P0 + G0。

- C2 = C1.P1 + G1 =(C0.P0 + G0).P1 + G1。

- C3 = C2.P2 + G2 =(C1.P1 + G1).P2 + G2。

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3。

Ci + 1を運ぶ方程式から、中間のキャリービットではなく、キャリーC0のみに依存することがわかります。

キャリー先見加算器-真理値表

回路図

上記の式は、AND、ORゲートとともに2レベルの組み合わせ回路を使用して実装されます。ここで、ゲートには複数の入力があると想定されています。

キャリー出力生成-キャリー先見加算器の回路

4ビットのキャリー先見加算器回路を以下に示します。

4ビット-キャリー-先見-加算器-回路-図

8ビットおよび16ビットのキャリー先見加算器回路は、4ビットの加算器回路をキャリーロジックとカスケード接続することで設計できます。

“正弦波を生成する方法 ”

キャリー先見加算器の利点

この加算器では、伝搬遅延が減少します。任意のステージでのキャリー出力は、開始ステージの最初のキャリービットにのみ依存します。この加算器を使用して、中間結果を計算することができます。この加算器は、計算に使用される最速の加算器です。

アプリケーション

高速キャリー先見加算器は、ICとして実装されたとおりに使用されます。したがって、加算器を回路に組み込むのは簡単です。 2つ以上の加算器を組み合わせることにより、より高いビットのブール関数の計算を簡単に行うことができます。ここでは、上位ビットに使用した場合、ゲート数の増加も中程度です。

この加算器では、面積と速度の間にトレードオフがあります。より高いビット計算に使用すると、高速になりますが、回路の複雑さも増し、回路が占める面積が増加します。この加算器は通常、より高度な計算に使用されるときに一緒にカスケードされる4ビットモジュールとして実装されます。この加算器は、他の加算器に比べてコストがかかります。

コンピューターでのブール計算では、加算器が定期的に使用されています。 Charles Babbageは、コンピュータのキャリービットを予測するメカニズムを実装して、 リップルキャリー加算器 。システムを設計する際、計算速度は設計者にとって最大の決定要因です。 1957年、Gerald B. Rosenbergerは、最新のBinary Carry Look-aheadAdderの特許を取得しました。ゲート遅延の分析とシミュレーションに基づいて、この加算器の回路をさらに高速化するように変更する実験が行われています。 nビットのキャリー先見加算器の場合、各ゲートの遅延が20の場合、伝搬遅延はどのくらいですか?

画像クレジット