バッファステージは基本的に強化された中間ステージであり、出力負荷の影響を受けることなく入力電流が出力に到達できるようにします。

この投稿では、デジタルバッファとは何かを理解しようとし、その定義、シンボル、トゥルーステーブル、ロジック「NOT」ゲートを使用したダブルインバージョン、デジタルバッファファンアウトファンイン、トライステートバッファ、同等のトライステートバッファスイッチ、アクティブ「HIGH」トライステートバッファ、アクティブ「HIGH」反転トライステートバッファ、アクティブ「LOW」状態トライステートバッファ、アクティブ「LOW」反転トライステートバッファ、トライステートバッファ制御、トライステートバッファデータバス制御。最後に、一般的に利用可能なデジタルバッファおよびトライステートバッファICの概要を説明します。

以前の投稿の1つで、デジタルインバーターとも呼ばれる論理「NOT」ゲートについて学びました。 NOTゲートでは、出力は常に入力を補完します。

したがって、入力が「HIGH」の場合、出力は「LOW」になり、入力が「LOW」の場合、出力は「HIGH」になります。これは、インバータと呼ばれます。

出力を入力から分離または分離する必要がある場合や、入力が非常に弱く、リレーやトランジスタなどを使用して信号の極性を反転せずに、より高い電流を必要とする負荷を駆動する必要がある場合があります。このような状況では、デジタルバッファが有用になり、信号ソースと実際のロードドライバステージの間のバッファとして効果的に適用されます。

そのような 論理ゲート 入力と同じ信号出力を提供し、中間バッファステージとして機能することができるものをデジタルバッファと呼びます。

デジタルバッファは、供給された信号の反転を実行せず、論理「NOT」ゲートのような「意思決定」デバイスでもありませんが、入力と同じ出力を出力します。

デジタルバッファのイラスト:

上記の記号は、三角形の先端に「o」がない論理「NOT」ゲートに似ています。つまり、反転は実行されません。

デジタルバッファのブール方程式はY = Aです。

「Y」は入力、「A」は出力です。

真理値表:

論理「NOT」ゲートを使用した二重反転:

デジタルバッファは、次の方法で2つの論理「NOT」ゲートを使用して構築できます。

入力信号は、最初に左側の最初のNOTゲートによって反転され、次に反転された信号は右側の次の「NOT」ゲートによってさらに反転されます。これにより、出力が入力と同じになります。

デジタルバッファが使用される理由

今、あなたはなぜデジタルバッファが存在するのか頭を悩ませているかもしれません、それは他の論理ゲートのような操作をしません、私たちは回路からデジタルバッファを捨ててワイヤーを接続することができます……。正しいですか?そうではありません。

これが答えです :論理ゲートは、操作を実行するために大電流を必要としません。低電流での電圧レベル(5Vまたは0V)で十分です。

すべてのタイプの論理ゲートは、主に内蔵アンプをサポートしているため、出力は入力信号に依存しません。 2つの論理「NOT」ゲートを直列にカスケード接続すると、出力ピンの入力と同じ信号極性が得られますが、電流は比較的大きくなります。言い換えれば、デジタルバッファはデジタルアンプのように機能します。

デジタルバッファは、信号発生器ステージとドライバステージ間の分離ステージとして使用できます。また、インピーダンスが回路に影響を与えるのを防ぐのにも役立ちます。

デジタルバッファは、スイッチングトランジスタをより効率的に駆動するために使用できるより高い電流能力を提供できます。

デジタルバッファは、「ファンアウト」機能とも呼ばれるより高い増幅を提供します。

デジタルバッファファンアウト機能:

扇形に広がります :ファンアウトは、デジタルバッファ(または任意のデジタルIC)によって並列に駆動できる論理ゲートまたはデジタルICの数として定義できます。

一般的なデジタルバッファのファンアウトは10です。これは、デジタルバッファが10個のデジタルICを並列に駆動できることを意味します。

ファンイン :ファンインは、デジタル論理ゲートまたはデジタルICが受け入れることができるデジタル入力の数です。

上記の回路図では、デジタルバッファのファンインは1で、これは1つの入力を意味します。 「2入力」論理「AND」ゲートには、2つのファンインなどがあります。

上記の回路図から、バッファは3つの異なる論理ゲートの3つの入力に接続されています。

上記の回路のバッファの代わりにワイヤを接続するだけでは、入力信号に十分な電流が流れておらず、ゲート間で電圧が低下し、信号を認識できない可能性があります。

したがって、結論として、デジタルバッファは、より高い電流出力でデジタル信号を増幅するために使用されます。

トライステートバッファ

これで、デジタルバッファの機能と、それが電子回路に存在する理由がわかりました。これらのバッファには、「HIGH」と「LOW」の2つの状態があります。 「トライステートバッファ」と呼ばれる別のタイプのバッファがあります。

このバッファには、「イネーブルピン」と呼ばれる追加のピンがあります。イネーブルピンを使用して、出力を入力に電子的に接続または切断できます。

通常のバッファと同様に、デジタルアンプとして機能し、入力信号と同じ出力信号を提供します。唯一の違いは、出力をイネーブルピンで電子的に接続および切断できることです。

したがって、3番目の状態が導入されます。この場合、出力は「HIGH」でも「LOW」でもありませんが、出力での開回路状態または高インピーダンスであり、入力信号に応答しません。この状態を「HIGH-Z」または「HI-Z」と呼びます。

上記はトライステートバッファの等価回路です。イネーブルピンは、出力を入力に接続または切断できます。

トライステートバッファには次の4つのタイプがあります。

•アクティブな「HIGH」トライステートバッファ

•アクティブな「LOW」トライステートバッファ

•アクティブな「HIGH」反転トライステートバッファ

•アクティブな「LOW」反転トライステートバッファ

それぞれを順番に見ていきましょう。

アクティブな「HIGH」トライステートバッファ

アクティブな「HIGH」トライステートバッファ(例:74LS241)では、イネーブルピンに「HIGH」または「1」または正の信号を印加すると、出力ピンが入力ピンに接続されます。

イネーブルピンに「LOW」または「0」または負の信号を印加すると、出力は入力から切り離されて「HI-Z」状態になり、出力は入力に応答せず、出力は開回路状態になります。

アクティブな「LOW」トライステートバッファ

ここで、イネーブルピンに「LOW」または「0」または負の信号を印加すると、出力が入力に接続されます。

「HIGH」、「1」、または正の信号を印加してピンを有効にすると、出力が入力から切断され、出力は「HI-Z」状態/開回路状態になります。

真理値表:

アクティブな「HIGH」反転トライステートバッファ

アクティブな「HIGH」反転トライステートバッファ(例:74LS240)では、ゲートは論理「NOT」ゲートとして機能しますが、イネーブルピンを備えています。

イネーブル入力に「HIGH」または「1」または正の信号を適用すると、ゲートがアクティブになり、出力が入力の反転/相補である通常の論理「NOT」ゲートのように動作します。

イネーブルピンに「LOW」または「0」または負の信号を印加すると、出力は「HI-Z」または開回路状態になります。

真理値表:

アクティブな「LOW」反転トライステートバッファ:

アクティブな「LOW」反転トライステートバッファでは、ゲートは論理「NOT」ゲートとして機能しますが、イネーブルピンを備えています。

「LOW」または「0」または負の信号を適用してピンを有効にすると、ゲートがアクティブになり、通常の論理「NOT」ゲートのように機能します。

イネーブルピンに「HIGH」または「1」または正の信号を印加すると、出力ピンは「HI-Z」状態/開回路状態になります。

真理値表:

トライステートバッファ制御:

上記のことから、バッファはデジタル増幅を提供でき、トライステートバッファはその出力を入力から完全に切断して開回路状態にすることができることがわかりました。

このセクションでは、トライステートバッファのアプリケーションと、データ通信を効率的に管理するためにデジタル回路でどのように使用されるかについて学習します。

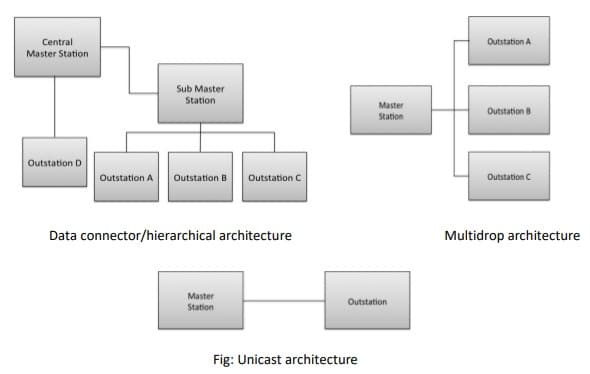

デジタル回路では、データを伝送するデータバス/ワイヤを見つけることができます。これらは、配線の混雑を減らし、PCBトレースを減らし、製造コストを削減するために、単一のバスであらゆる種類のデータを伝送します。

バスの両端には、複数のロジックデバイス、マイクロプロセッサ、およびマイクロコントローラが接続されており、相互に同時に通信を試みて、競合と呼ばれるものを作成します。

バス内の一部のデバイスが「HIGH」を駆動し、一部のデバイスが同時に「LOW」を駆動すると、回路内で競合が発生し、短絡が発生して回路が損傷します。

トライステートバッファは、このような競合を回避し、バスを介してデータを適切に送受信できます。

トライステートバッファは、データバス内でロジックデバイス、マイクロプロセッサ、およびマイクロコントローラを相互に分離するために使用されます。デコーダーは、1セットのトライステートバッファーのみがバスを介してデータを渡すことを許可します。

データセット「A」がマイクロコントローラに接続され、データセット「B」がマイクロプロセッサに接続され、データセット「C」がいくつかの論理回路に接続されているとします。

上記の回路図では、すべてのバッファがアクティブハイトライステートバッファです。

デコーダーがENAを「HIGH」に設定すると、データセット「A」が有効になり、マイクロコントローラーはバスを介してデータを送信できるようになります。

残りの2つのデータセット「B」と「C」は「HI-Z」または非常に高インピーダンスの状態にあり、マイクロプロセッサと論理回路をバスから電気的に分離します。バスは現在マイクロコントローラで使用されています。

デコーダがENB「HIGH」を設定すると、データセット「B」はバスを介してデータを送信でき、残りのデータセット「A」と「C」は「HI-Z」状態でバスから分離されます。同様に、データセット「C」が有効になっている場合。

データバスは、競合を防ぐために、特定の時間にデータセット「A」、「B」、または「C」のいずれかによって使用されます。

また、2つのトライステートバッファを並列および反対方向に接続することにより、デュプレックス(双方向)通信を確立することもできます。イネーブルピンは方向制御として使用できます。このような種類のアプリケーションには、IC74245を利用できます。

一般的に利用可能なデジタルバッファとトライステートバッファのリストは次のとおりです。

•74LS07Hex非反転バッファー

•74LS1716進バッファー/ドライバー

•74LS244オクタルバッファ/ラインドライバ

•74LS245オクタル双方向バッファ

•CD4050Hex非反転バッファー

•CD450316進トライステートバッファ

•HEF40244トライステートオクタルバッファ

これで、デジタルバッファのしくみと、さまざまなデジタル構成に関する説明は終わりです。詳細をよく理解するのに役立つことを願っています。他にご質問やご提案がございましたら、コメント欄にご質問をお寄せください。すぐに返信があります。

前:論理ゲートのしくみ 次へ:図と式を使用したプルアップ抵抗とプルダウン抵抗の理解