ザ・ フェーズロックループ は、現代の電子システムの基本ブロックの1つです。これは通常、マルチメディア、通信、およびその他の多くのアプリケーションで使用されます。 PLLには、線形と非線形の2種類があります。非線形は現実の世界で設計するのが難しく複雑ですが、線形制御理論はアナログPLLでうまくモデル化されています。 PLLは、ほとんどの電子アプリケーションに線形モデルで十分であることを証明しています。

フェーズロックループとは何ですか?

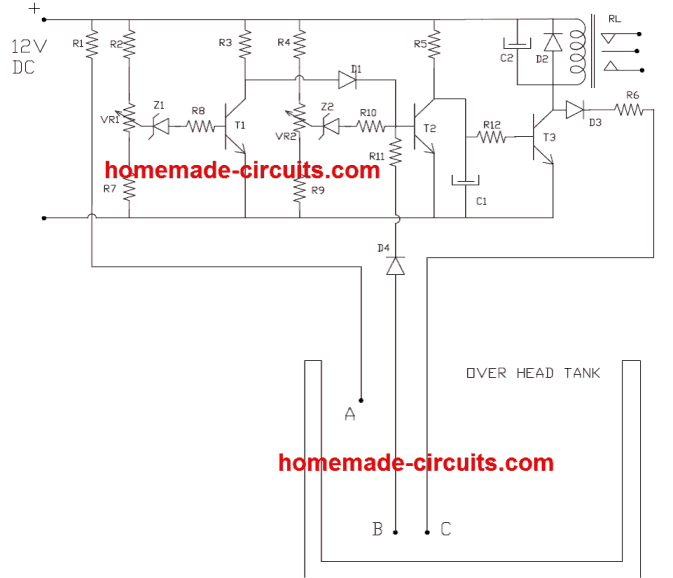

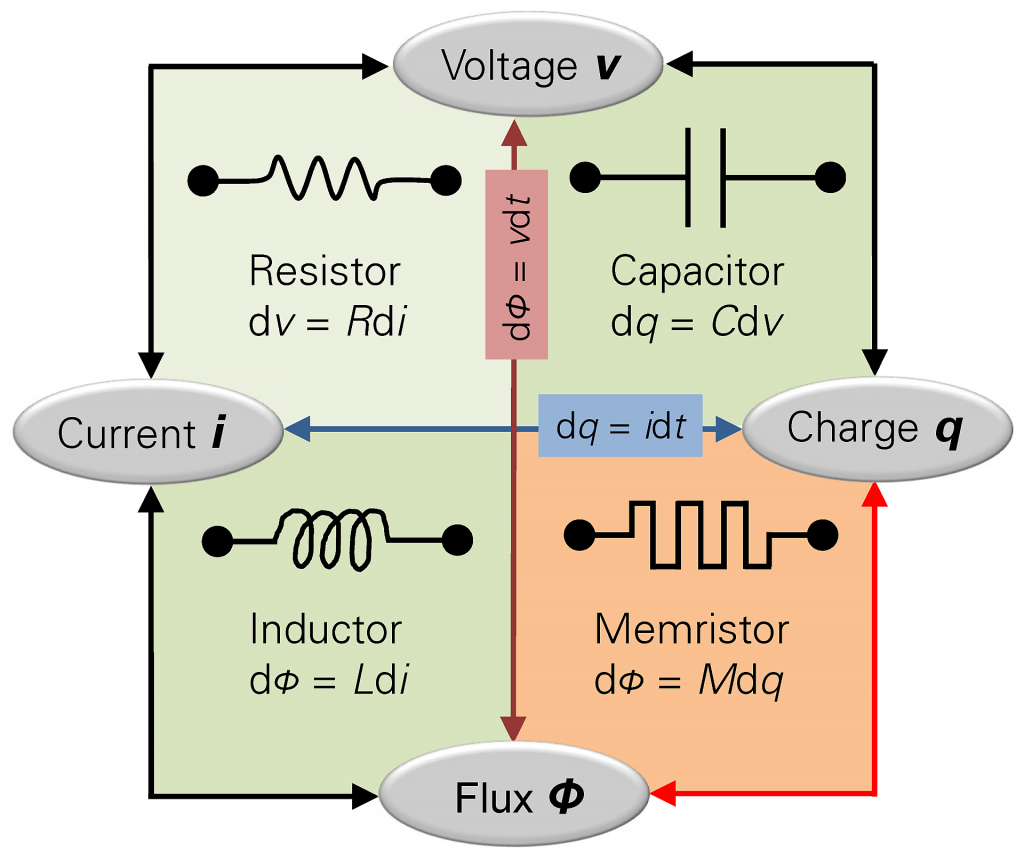

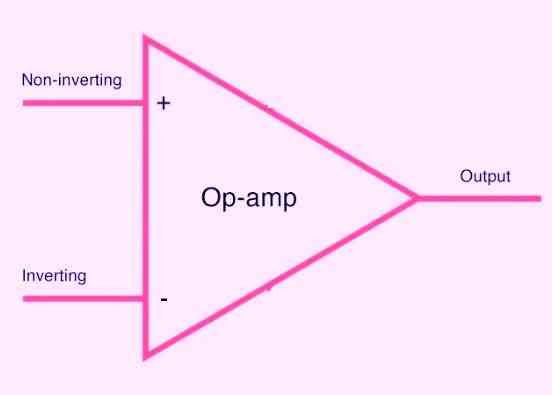

フェーズロックループは、位相検出器と電圧制御発振器で構成されています。位相検出器の出力は電圧制御発振器(VCO)の入力であり、VCOの出力は以下の基本ブロック図に示されている位相検出器の入力の1つに接続されています。これらの2つのデバイスが相互にフィードされると、ループが形成されます。

フェーズロックループの基本図

PLLのブロック図と動作原理

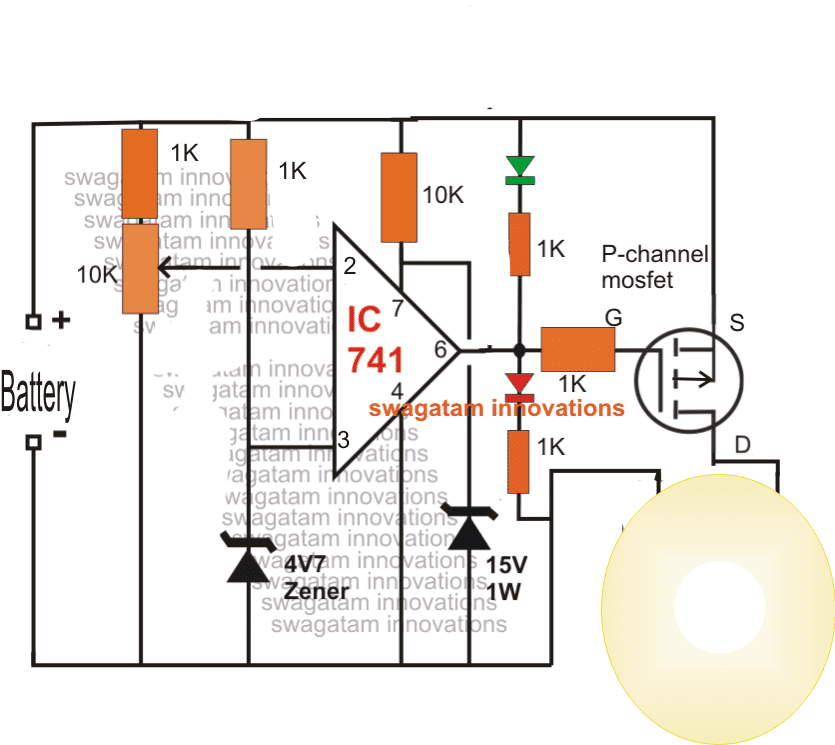

フェーズロックループは、位相検出器、 電圧制御発振器 そして、それらの間に、ローパスフィルターが固定されています。入力周波数「Fi」の入力信号「Vi」は、位相検出器によって許可されます。基本的に位相検出器は コンパレータ これは、入力周波数fiとフィードバック周波数foを比較します。位相検出器の出力は、DC電圧である(fi + fo)です。位相検出器の位相がずれている、つまりDC電圧がローパスフィルター(LPF)に入力され、高周波ノイズが除去され、安定したDCレベル(Fi-Fo)が生成されます。 VfはPLLの動的特性でもあります。

PLLブロック図

ローパスフィルターの出力、つまりDCレベルはVCOに渡されます。入力信号は、VCOの出力周波数(fo)に正比例します。入力周波数と出力周波数は、出力周波数が入力周波数と等しくなるまで、フィードバックループを介して比較および調整されます。したがって、PLLはフリーランニング、キャプチャ、およびフェーズロックのように機能します。

入力電圧が印加されていない場合は、自走ステージと呼ばれます。 VOCに適用される入力周波数が変化し、比較のために出力周波数が生成されるとすぐに、それはキャプチャステージと呼ばれます。次の図は、PLLのブロック図を示しています。

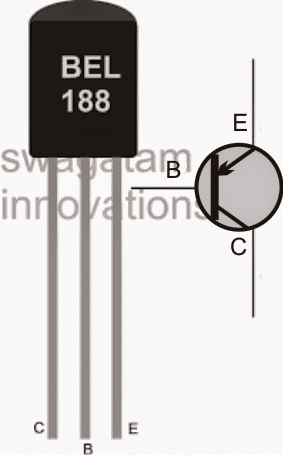

フェーズロックループ検出器

フェーズロックループ検出器は、VCOの入力周波数と出力周波数を比較して、2つの周波数の位相差に正比例するDC電圧を生成します。アナログ信号とデジタル信号は、フェーズロックループで使用されます。モノリシックPLLのほとんど 集積回路 アナログ位相検出器を使用し、位相検出器の大部分はデジタルタイプのものです。二重平衡混合回路は、アナログ位相検出器で一般的に使用されます。いくつかの一般的な位相検出器を以下に示します。

排他的論理和位相検出器

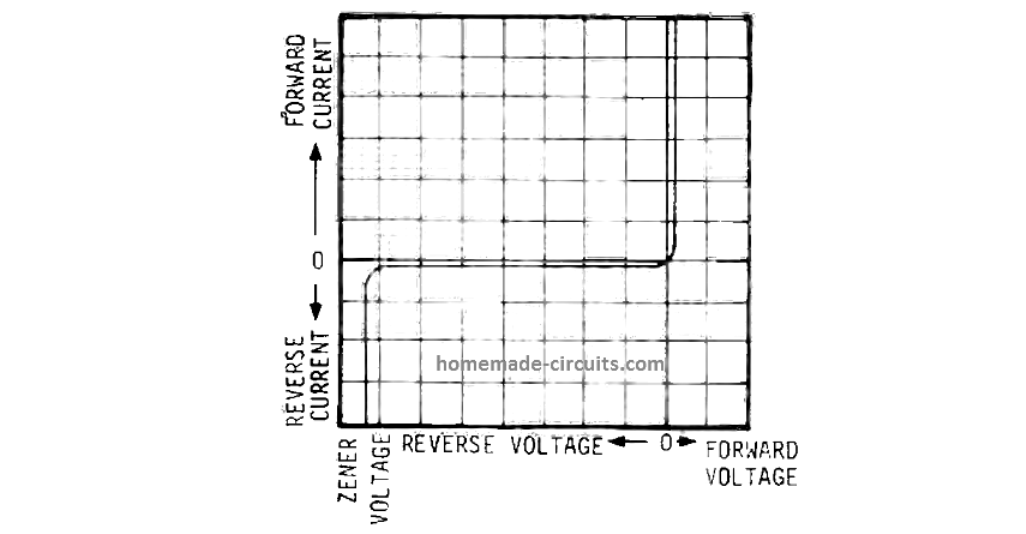

専用のOR位相検出器はCMOSIC4070タイプです。入力周波数と出力周波数は、EXOR位相検出器に適用されます。高い出力を得るには、少なくとも1つの入力が低く、他の出力条件が低い必要があります。これを以下の真理値表に示します。波形、入力周波数と出力周波数を考えてみましょう。つまり、fiとfoの位相差は0度です。その場合、コンパレータのDC出力電圧は、2つの入力間の位相差の関数になります。

| あります | fo | Vdc |

低 | 低 | 低 |

低 | 高い | 高い |

高い | 低 | 高い |

高い | 高い | 低 |

fiとfoの位相差の関数は、DC出力電圧のグラフに示されているとおりです。位相検出器が180度の場合、出力電圧は最大になります。入力周波数と出力周波数の両方が方形波の場合、これらのタイプの位相検出器が使用されます。

排他的論理和位相検出器

エッジトリガー位相検出器

エッジトリガー位相検出器は、入力周波数と出力周波数がパルス波形であり、デューティサイクルが50%未満の場合に使用されます。 R-Sフリップフロップは、次の図に示す位相検出器に使用されます。 R-Sからへ フリップ・フロップ 、2つのNORゲートは相互結合されています。位相検出器の出力は、R-Sフリップフロップをトリガーすることによって論理状態を変更できます。入力周波数と出力周波数の立ち上がりエッジにより、位相検出器の出力が変化する可能性があります。

エッジトリガー位相検出器

モノリシック位相検出器

モノリシック位相検出器は、CMOSタイプ、つまりIC 4044です。これは、高調波感度から高度に補償され、回路は入力信号の遷移にのみ応答できるため、デューティサイクルの問題は回避されます。重要なアプリケーションでは、これは最も熱狂的な位相検出器です。振幅の独立した変動には、入力波形の位相エラー、出力エラー電圧、およびデューティサイクルがありません。

フェーズロックループのアプリケーション

- FM操作用のFM復調ネットワーク

- それはで使用されます モーター速度制御 と追跡フィルター。

- これは、復調キャリア周波数の周波数シフトデコードで使用されます。

- それはデジタルコンバーターに間に合うように使用されます。

- ジッタ低減、スキュー抑制、クロックリカバリに使用されます。

これはすべて、フェーズロックループの動作原理と動作原理およびそのアプリケーションに関するものです。この記事に記載されている情報が、プロジェクトについて何かを知り、理解するのに役立つことを願っています。さらに、この記事や 電気および電子プロジェクト 以下のセクションでコメントできます。ここにあなたへの質問があります、安定性のためにPLLをシミュレートするための最良の方法は何ですか?

写真クレジット:

- PLLのブロック図 今日のサーキット

- 排他的論理和位相検出器 sanfoundry

- エッジトリガー位相検出器 LEARNABOUT-ELECTRONICS