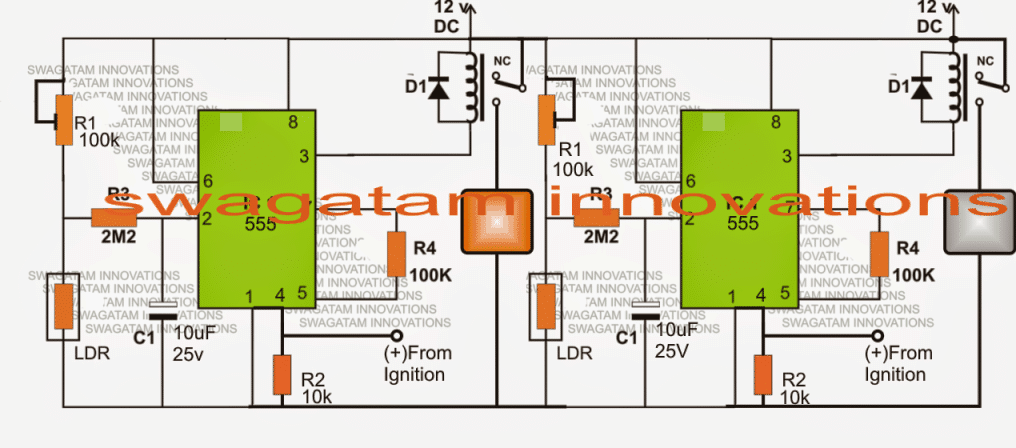

ラッチ/リセットネットワークのセットを使用すると、交互の入力クロックに応答して、ロジックを順方向に移動させ、特定の出力セットをHIGHに切り替えることが可能になります。そして、最大制限に達すると、入力クロックはシャットダウンを開始するか、逆の順序でシーケンスを撤回し始めます。

したがって、アップダウンシーケンスは、単一の発振入力クロック信号によって制御されます。

このプロセスは、次のように説明することもできます。

適用されたスイッチングクロックに応答して、回路は増分シーケンスで出力にHIGHロジックを追加し始め、最大制限に達すると、適用されたシーケンスに応答して、反対のシーケンスで出力をLOWにすることにより、出力からHIGHを減算し始めます。クロック信号。

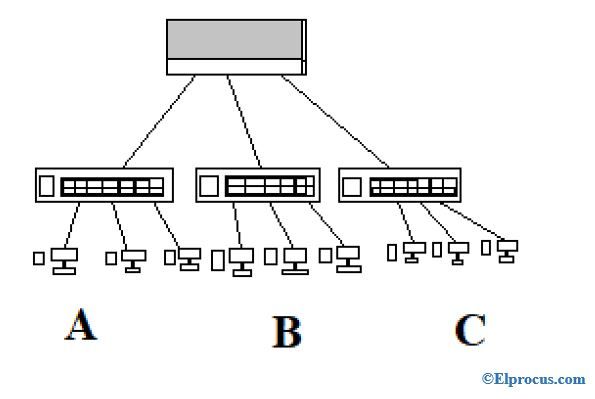

ここでは、4つの出力のみが示されています。 IC4043には4対のセット/リセットラッチしかありません それでも、IC 4017をカスケード接続し、既存のICに別の4043 ICを追加することで、数を増やすことができます。これにより、8つの数値シーケンスセット/リセットまたは8ペアのアップ/ダウン出力を取得できます。

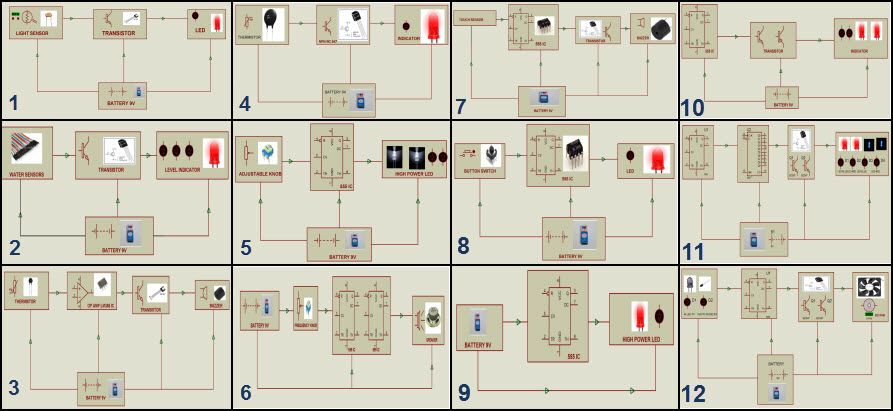

応用

この回路は、最大制限を超えるとすぐにパラメータのそれ以上の増加が抑制され、逆に制限が範囲内に戻るとプロセスが復元されて開始されるように、特定のパラメータを制御するのに非常に役立ちます。

たとえば、小型エレベータに適用して3人だけがリフト内に入ることができます。この制限を超えると、エレベータの起動は禁止されますが、制限が回復すると、エレベータは移動できます。

このUP / DOWNシーケンサーのしくみ

この回路は元々、電源装置を順番に起動し、その後、反対の順序でもう一度電源を切るために作成されました。この機能は、電力を使用して特定の順序で取り出す必要がある機器や回路をいじくり回す場合に役立つことがよくあります。

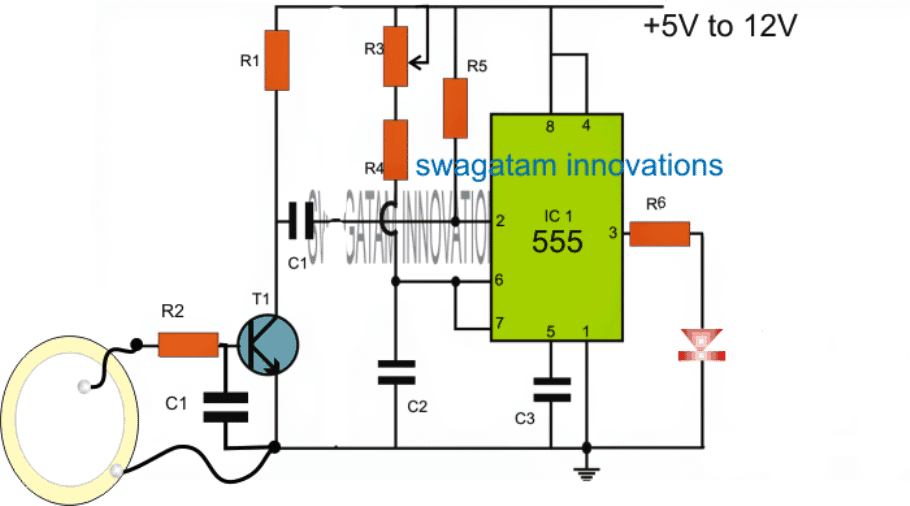

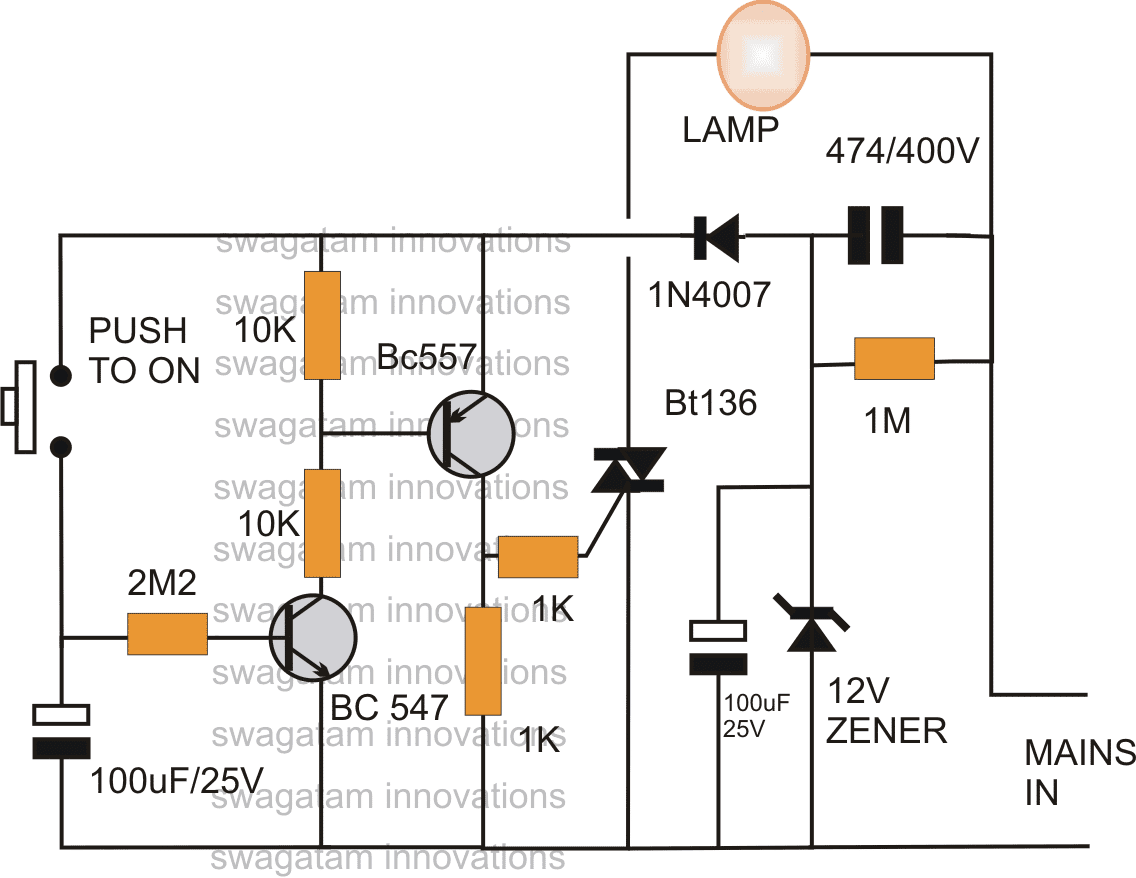

回路の主要なセクションは、主力のIC 4017CMOSディケードカウンターです。出力Q1からQ4は、1-2-3-4の順序で連続してラッチを確立することに慣れており、その後、カウントが停止します。スイッチS1を押すと、カウントが続行され、カウンタ出力Q5〜Q8が適用されて、逆の順序、つまり4-3-2-1の順序でラッチがリセットされます。最後の出力Q9は、カウンターを停止するために使用されます。

電源がオンになるとすぐに、C2とR2は最初にカウンタをリセット位置にします。電源電圧が安定すると、リセット信号は最終的にローになり、4017はIC1d、R3、およびC3で構成される発振器を介して取得される1Hzのクロック信号でカウントを開始できます。

ザ・ IC4017の出力ピン クロックパルスの立ち上がりエッジごとに連続してトリガーされますが、次のクロックパルスが到着すると、最後の出力がシャットダウンします。

クワッドRSラッチタイプ4043のラッチにより、出力をアクティブのままにすることができます。 IC1bがIC1aを介してピン13のクロックイネーブル信号を除去するため、IC2はQ4でカウントを停止します。

4017がカウントを続行し、出力をオフにできるようにするには、S1を押す必要があります。これにより、ピン13でクロックイネーブルが再確立されます。

カウンタ出力Q5〜Q8はラッチのリセット入力に接続されているため、IC2シーケンスが下に移動すると、ラッチは逆方向にリセットされます。カウントプロセスは最終的にIClcによってQ9で停止され、IClcは再びクロックイネーブル信号を取り除きます。

未定義の始動状況を回避するために、ラッチの「リセット」入力に高値、低電流のプルアップ抵抗(R4〜R7)が採用されています。

パーツリスト

抵抗器(すべての抵抗器は1/4ワット5%です)

R1 = 4K7

R3 = 4M7

R2、R4、R5、R6、R7 = 1M

コンデンサ

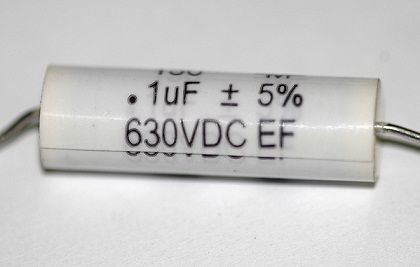

C1、C4、C5 = 0.1uF /セラミック

C2 = 22uF / 25V

C3 = 1uF / 25V

集積回路

IC 4017 = 1no

IC 4043 = 1no

IC 4093 = 1no

S1 = ONスイッチにプッシュ

前:オートバイのボタンがロック回路を開始する 次へ:トランジスタのDCバイアス– BJT