足し算と引き算は、デジタルシステムの基本的な操作です。 制御システム & デジタル信号処理 。これらのシステムは、正確で高速な操作を提供することにより、加算器と減算器の影響を受けます。加算器と減算器は、乗算、減算、除算などの他のデジタル演算で広く使用されているため、デジタルシステムで重要な役割を果たします。したがって、これらのパフォーマンスを向上させると、回路内での二項演算の実行が進みます。デジタル回路の性能は、動作速度、レイアウト面積、消費電力を評価することで見積もることができます。この記事では、並列加算器と並列減算器の概要について説明します。

並列加算器と並列減算器とは何ですか?

パラレル 加算器 並列減算器は、主にその定義、動作、長所と短所について説明します。

並列加算器とは何ですか?

2つの2進数とi / pキャリーの加算を実行するために使用されるデジタル回路。1つのビットの長さが別のビットよりも長く、同等のビットのペアと並列に動作します。並列加算器の配置は、全加算器(FA)をチェーンモデルに配置することで実行できます。 全加算器 (FA1)は、チェーン内の次の全加算器(FA2)のキャリーi / pにリンクできます。並列加算器の図を以下に示します。

並列加算器

nビット並列加算器の操作は、n全加算器を使用して実行できます。同様に、2ビット並列加算器の場合、2つの加算器が必要です。一般的に、これらの加算器には次のロジックが含まれます。 キャリー先見 次のステージの追加の間でのキャリーの伝播が追加の速度を制限しないことを確認するため。

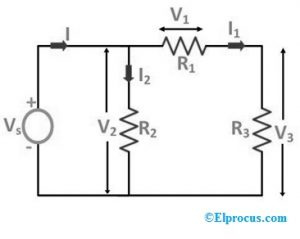

“可変抵抗器の配線方法 ”

並列加算器の動作

並列加算器の図を上に示します。その中で、FA1のような最初の全加算器は、A1とB1にキャリー「C1」を加算することで「S1」のような合計を生成できます。「C2」キャリーはチェーンの2番目の加算器に接続されます。

その後、FA2のような2番目の全加算器は、「C2」キャリービットを使用してA2およびB2入力ビットを挿入し、S2およびC3キャリーの合計を生成します。同様に、このプロセスは、n番目の全加算器がCnキャリービットを使用してAn&Bnなどの入力を挿入し、Coutでo / pの最後のビット(最後のキャリービット)を生成するまで、残りの全加算器に対して続行されます。

並列減算器とは何ですか?

ビットの2つのバイナリペア間の算術差を計算するために使用されるデジタル回路は、並列減算器として知られています。ここでバイナリビットでは、1ビットの長さが他のビットよりも長くなります。この減算器の設計は、すべての完全減算器、半分と完全な減算器、またはすべてのFAと減数補数のi / pの組み合わせなど、さまざまな方法で行うことができます。並列減算器の図を以下に示します。

並列減算器

nビット並列減算器では、n個の完全減算器をカスケード接続することで目的のo / pを実現できます。これの接続は、4ビット並列加算器に似ています。これの減算は、各ビットからその並列ビットに実行できます。借用が生成された場合、それはのカスケード中に伝播します 完全減算器 。

並列減算器の動作

上記の並列減算図に示されているように、減算器は、すべてのFAと減数補数i / pの組み合わせで配置できます。

減算の手順は、減数の2の補数を使用した被減数の加算を検討することで実行できます。並列減算ができるように。

数値の2の補数は、2進数を1の補数に変換することで実行できます。ここで1の補数は、2進数を否定することです。ここで、1の補数のLSBビットに1を加算することにより、2の補数を得ることができます。

を使用して 論理ゲート 、「B」の1の補数は、NOT論理ゲートを介して取得できます。「1」はキャリー全体に追加され、「B」の2の補数を取得します。さらに、これを「A」に加算して算術減算を実行します。

“1.5 vDC電源 ”

この手順は、「FAn」のような最後の全加算器まで続き、キャリービット「Cn」を使用してi / p「An」と2の補数「Bn」を含め、最後のo / pビットを生成します。最終キャリービット「Cout」。

利点

ザ・ 並列加算器と減算器の利点 以下のものが含まれます。

- この加算器または減算器の動作は、シリアル加算器または減算器とは対照的に高速です。

- 加算に必要な時間は、ビットの桁数に依存しません。

- この中のすべてのビットは一度に加算または減算されるため、o / pは並列形式になります。

- 高価ではありません。

- これらは、シリアル版と比較して高速です。

並列加算器/並列減算器のデメリット

ザ・ 並列加算器と減算器の欠点 以下のものが含まれます。

- チェーンプロセスでは、各全加算器は前の加算器のキャリーを待つ必要があります。

- チェーンプロセスのすべての加算器/減算器は、ポートへの入力を即座に取得します。ただし、キャリーやボローなどのポートは、前の加算器/減算器がプロセスを完了するまで、i / psを取得しません。

- そのため、遅延が発生しているので、一度は合計されません。 FAまたは完全減算器の数が増加します。

- 追加の過程での以前のキャリーは含まれません。

- したがって、マルチビット加算で使用されるカスケードには適していません。

- チェーン構成内でFAを使用すると、出力ドライブの機能が低下する可能性があります。

よくある質問

1)。加算器とは何ですか?

数値の加算を実行するために使用されるデジタル回路

“可変速DC電気モーター ”

2)。減算器とは何ですか?

2つの2進数間の非類似度を計算するために使用される電子論理回路。

3)。加算器の種類は何ですか?

それらは、半加算器、全加算器、およびマルチビット加算器です。

4)。マルチビット加算器とは何ですか?

それらは、シリアル加算器とパラレル加算器です。

したがって、これはすべてパラレルの概要に関するものです 加算器と減算器 、およびそれらの長所と短所。加算器と減算器は、コンピューターの算術論理演算装置で加算を計算するために、またCPUとGPUでグラフィックスを使用して回路の複雑さを軽減するために広く使用されています。ここにあなたへの質問があります、加算器と減算器の違いは何ですか?