エレクトロニクスの分野では、すべてのコンポーネントが機能する最も重要な概念は「 論理ゲート 「。論理ゲートの概念は、集積回路、センサー、スイッチングの目的、マイクロコントローラーとプロセッサー、暗号化と復号化の目的など、すべての機能に実装されています。これらに加えて、論理ゲートの幅広いアプリケーションがあります。加算器、減算器、全数など、多くの種類の論理ゲートがあります。 加算器 、Full Subtractor、Half Subtractor、およびその他多数。したがって、この記事はの集合的な情報を提供します ハーフサブトラクタ回路 、 半減算真理値表 、および関連する概念。

Half Subtractorとは何ですか?

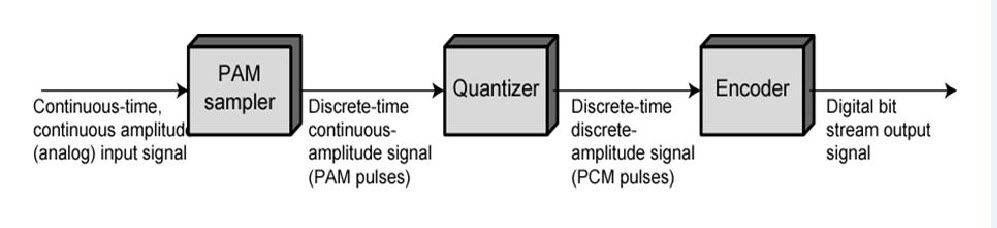

ハーフ減算器について説明する前に、バイナリ減算について知っておく必要があります。バイナリ減算では、減算のプロセスは算術減算に似ています。算術減算では、2進数システムが使用されますが、2進数減算では、2進数が減算に使用されます。結果の項は、差と借用で表すことができます。

ハーフサブトラクタが最も重要です 組み合わせ論理回路 で使用されています デジタルエレクトロニクス 。基本的には電子機器、言い換えれば論理回路と言えます。この回路は、2桁の2進数の減算を実行するために使用されます。前回の記事では、すでに説明しました 半加算器と全加算器回路の概念 計算に2進数を使用します。同様に、減算回路は減算に2進数(0,1)を使用します。ハーフサブトラクタの回路は2つで構築できます 論理ゲート、すなわちNANDおよびEX-ORゲート 。この回路は、差と借用などの2つの要素を提供します。

2進数の減算と同様に、長桁は1ですが、減算1は被減数0よりも優れているので、借用を生成できます。このため、借用が必要になります。次の例は、2つのバイナリビットのバイナリ減算を示しています。

最初の桁 | 2桁目 | 差 | 借りて |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

上記の減算では、2桁をAとBで表すことができます。これらの2桁を減算して、結果のビットを差と借用として与えることができます。

最初の2行と4行、これらの行の差を観察すると、減算は被減数よりも小さいため、差と借用は類似しています。同様に、3番目の行を観察すると、被減数から被減数が差し引かれます。したがって、減算桁が被減数桁よりも優れているため、差分ビットと借用ビットは1です。

この組み合わせ回路は、あらゆる種類の必須ツールです。 デジタル回路 入力と出力の可能な組み合わせを知るため。たとえば、減算器に2つの入力がある場合、結果の出力は4つになります。ハーフ減算器のo / pは、以下の表に記載されており、差分ビットと借用ビットを示します。回路の真理値表の説明は、EX-OR論理ゲートやANDゲート操作の後にNOTゲートなどの論理ゲートを使用して行うことができます。

を使用して真理値表を解く Kマップ 以下に示します。

半減算器kマップ

ザ・ 半減算式 真理値表とKマップを使用すると、次のように導出できます。

差 (D)=( x’y + xy ')

= x⊕y

借りる(B)= x’y

論理回路

ザ・ 半減算論理回路 論理ゲートを使用して説明できます。

- 1XORゲート

- 1ゲートではありません

- 1ANDゲート

表現は

ハーフ減算器論理回路

半減算器のブロック図

ハーフサブトラクタのブロック図を上に示します。 2つの入力が必要であり、2つの出力があります。ここでは、入力はA&Bで表され、出力は差異と借入です。

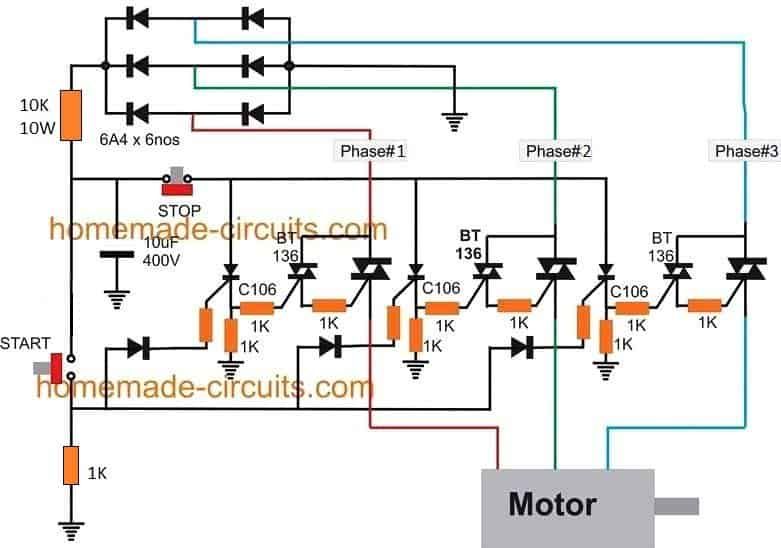

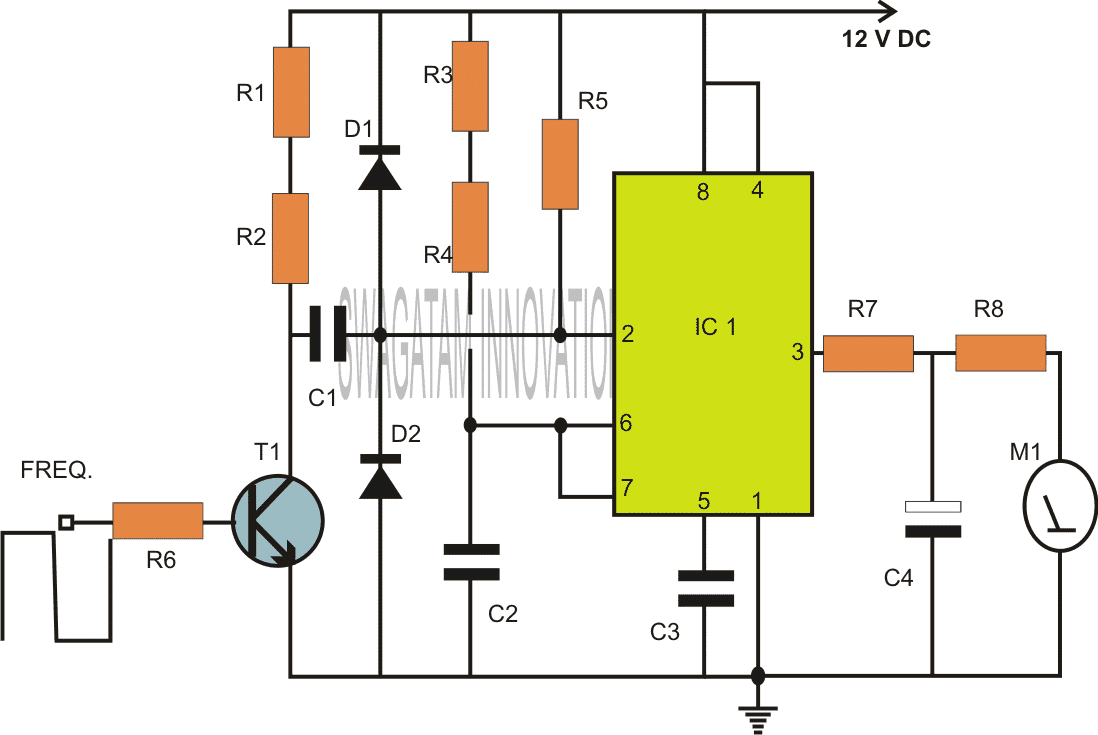

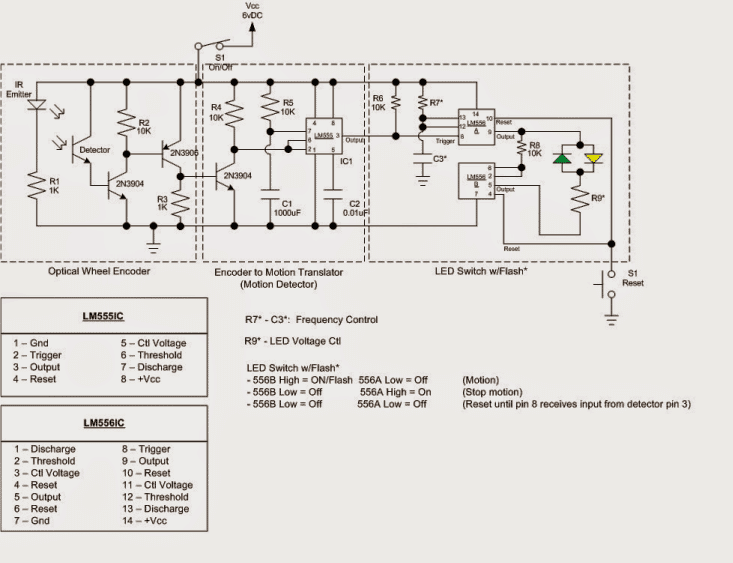

上記の回路は、EX-ORおよびNANDゲートを使用して設計できます。ここで、NANDゲートは、ANDゲートとNOTゲートを使用して構築できます。したがって、半分の減算回路を作成するには、EX-ORゲート、NOTゲート、NANDゲートの3つの論理ゲートが必要です。

ANDゲートとNOTゲートを組み合わせると、NANDゲートという名前の異なる組み合わせゲートが生成されます。同じ入力A&Bの場合、Ex-ORゲート出力は差分ビットになり、NANDゲート出力は借入ビットになります。

ANDゲート

ANDゲートは、複数の入力と単一の出力を備えたデジタル論理ゲートの一種であり、入力の組み合わせに基づいて論理積を実行します。このゲートのすべての入力がハイの場合、出力はハイになり、そうでない場合、出力はローになります。真理値表付きANDゲートの論理図を以下に示します。

ANDゲートと真理値表

“ビオ・サバール法の例 ”

ゲートではありません

NOTゲートは、単一の入力を備えたデジタル論理ゲートの一種であり、入力に基づいて出力が反転されます。たとえば、NOTゲートの入力がハイの場合、出力はローになります。真理値表を使用したNOTゲートの論理図を以下に示します。このタイプの論理ゲートを使用することにより、NANDおよびNORゲートを実行できます。

ゲートと真理値表ではありません

元ORゲート

排他的論理和または排他的論理和ゲートは、2入力と単一出力を備えたデジタル論理ゲートの一種です。この論理ゲートの動作は、ORゲートに依存します。このゲートの入力のいずれかがハイの場合、EX-ORゲートの出力はハイになります。 EX-ORの記号と真理値表を以下に示します。

XORゲートと真理値表

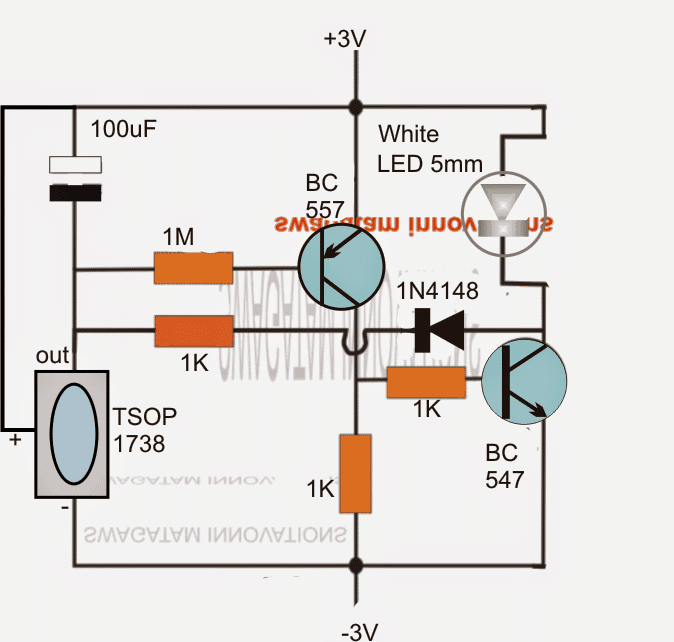

ナンドゲートを使用したハーフ減算回路

減算器の設計は、 論理ゲートの使用 NANDゲートとEx-ORゲートのように。この半減算回路を設計するには、2つの概念、つまり差と借用を知る必要があります。

ナンドゲートを使用したハーフ減算回路

注意深く監視すると、この回路によって実行されるさまざまな操作がEX-ORゲートの操作に正確に関連していることはかなり明らかです。したがって、EX-ORゲートを使用して違いを生み出すことができます。同様に、半加算回路によって生成される借用は、ANDゲートやNOTゲートなどの論理ゲートのブレンドを使用することで簡単に実現できます。

このHSは、構築に5つのNORゲートが必要なNORゲートを使用して設計することもできます。 NORゲートを使用した回路図の半減算器は次のように示されます。

NorGatesを使用したハーフ減算器

真理値表

最初のビット | セカンドビット | 差 (EX-ORアウト) | 借りて (NANDアウト) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

VHDLおよびテストベンチコード

ハーフサブトラクタのVHDLコードは次のように説明されています。

ライブラリIEEE

IEEE.STD_LOGIC_1164.ALLを使用します

IEEE.STD_LOGIC_ARITH.ALLを使用します

IEEE.STD_LOGIC_UNSIGNED.ALLを使用します

エンティティHalf_Sub1は

ポート(a:STD_LOGIC内

b:STD_LOGIC内

HS_Diff:アウトSTD_LOGIC

HS_Borrow:out STD_LOGIC)

Half_Sub1を終了します

Half_Sub1のアーキテクチャの動作は

ベギン

HS_Diff<=a xor b

HS_Borrow<=(not a) and b

ザ・ HSのテストベンチコード 以下のように説明されています:

図書館IEEE

ieee.std_logic_1164.ALLを使用します

ENTITY HS_tb IS

END HS_tb

HS_tbのアーキテクチャHS_tbは

コンポーネントHS

PORT(a:IN std_logic

b:STd_logicで

HS_Diff:OUT std_logic

HS_Borrow:OUT std_logic

)

エンドコンポーネント

シグナルa:std_logic:= ‘0’

シグナルb:std_logic:= ‘0’

シグナルHS_Diff:std_logic

“ダイオード整流器とは ”

シグナルHS_Borrow:std_logic

ベギン

新規:HSポートマップ(

a => a、

b => b、

HS_Diff => HS_Diff、

HS_borrow => HS_borrow

)

stim_proc:プロセス

ベギン

に<= ‘0’

b<= ‘0’

30ns待つ

に<= ‘0’

b<= ‘1’

30ns待つ

に<= ‘1’

b<= ‘0’

30ns待つ

に<= ‘1’

b<= ‘1’

待つ

最終過程

終わり

ハーフ減算器を使用したフル減算器

完全減算器は、2ビットを使用して減算機能を操作する組み合わせデバイスであり、被減数と減数です。回路は前の出力の借用を考慮し、2つの出力を持つ3つの入力があります。 3つの入力は被減数、減算、および前の出力から受け取った借用である入力であり、2つの出力は差と借用です。

完全な減算器の論理図

の真理値表 完全減算器 です

| 入力 | 出力 | |||

| バツ | Y | 陰 | FS_Diff | FS_Borrow |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

上記の真理値表を使用して、ハーフサブトラクタを使用してフルサブトラクタを実装するための論理図と回路図を以下に示します。

HSを使用した完全減算器

ハーフサブトラクタの利点と制限

ハーフサブトラクタの利点は次のとおりです。

- この回路の実装と構築はシンプルで簡単です

- この回路は、デジタル信号処理で最小限の電力を消費します

- 計算機能は、改善された速度で実行できます

この組み合わせ回路の制限は次のとおりです。

多くの操作や機能でハーフ減算器の広範なアプリケーションがありますが、いくつかの制限があり、それらは次のとおりです。

- ハーフサブトラクタ回路は、これがこの回路の重大な欠点である前の出力からの「ボローイン」を受け入れません。

- 多くのリアルタイムアプリケーションは多数のビットの減算で動作するため、ハーフサブトラクタデバイスは多くのビットを減算する機能を備えていません。

ハーフサブトラクタのアプリケーション

ハーフサブトラクタのアプリケーションには、次のものがあります。

- ハーフサブトラクタは、オーディオまたはラジオ信号の力を減らすために使用されます

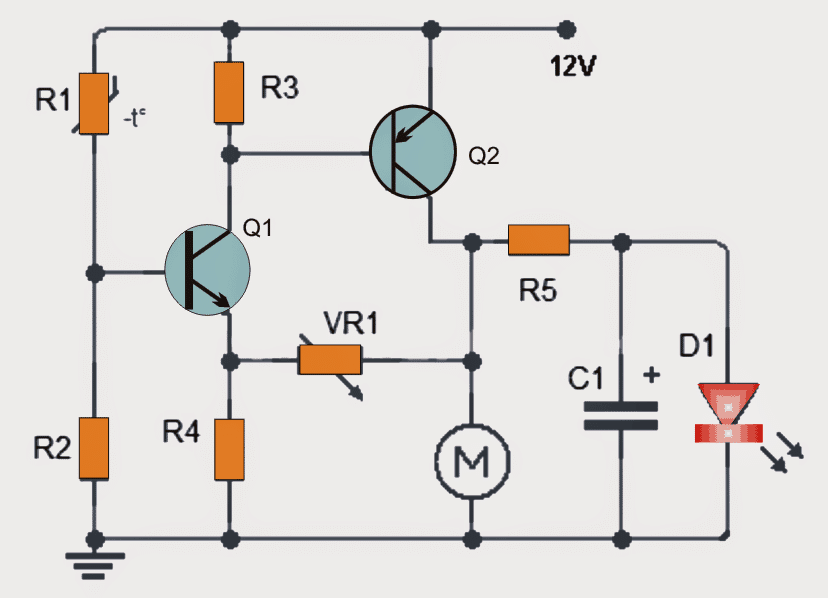

- かもね アンプで使用 音の歪みを減らすために

- 半減算器は プロセッサのALUで使用

- 演算子を増減したり、アドレスを計算したりするために使用できます

- ハーフ減算器は、最下位の列番号を減算するために使用されます。複数桁の数値の減算には、LSBに使用できます。

したがって、上記の半減算理論から、最後に、この回路を使用して、あるバイナリビットから別のバイナリビットから減算して、DifferenceやBorrowなどの出力を提供できることを閉じることができます。同様に、NANDゲート回路とNORゲートを使用してハーフサブトラクタを設計できます。知られている他の概念は何ですか ハーフサブトラクタVerilogコード RTLスケマティックダイアグラムをどのように描画できますか?