この投稿では、10個の高出力アンプを順次オンにするために使用される10ステップの順次スイッチングラッチ回路を作成する方法を学習します。アイデアはジェリーB.ウィリアムズ氏によって要求されました

パワーアンプを順番にオンにする回路

回路の目的と要件

- 私の回路の質問は、あなたが本当に知りたいよりも詳細になりますが、私のアプリケーション全体を理解していただきたいと思います。うまくいけば、あなたは私の努力でここで私を助けることができるでしょう!!!まず…..私は–ではなく–回路設計者です!!!私は電子機器の–ビルダー–です。回路図を教えていただければ、PCBを設計できます。PCBが入るメカニカルシャーシも設計できます。

- しかし、私はすべての電子部品について理解していません。

- 私の回路アプリケーションは、アリーナやスタジアムでのコンサート用のサウンド強化システムで使用される高出力オーディオパワーアンプを順次電源オンするために使用されます。

- アンプは19インチラックに取り付けられており、AC電源がラックに供給されると、すべてのアンプが同時にオンになるのではなく、時間遅延を伴ってアンプが順番にオンになるようにします。 。

- アンプ自体は、大電流ソリッドステートリレー(つまりLED)によって制御されます。それで、これが私が入手したいものです…..

- 10個のLEDを駆動できるシーケンシャルパワーオン回路の回路図。回路がDC電圧でパワーアップされると、回路が安定するまで3〜5秒の遅延が発生し、最初の「オン」パルスが開始されて最初のLED(実際には内部にあります)がオンになります。ソリッドステートリレー)。 –すべて–最終的に電源が「オフ」になるまで、すべてのLEDは「オン」のままになります!!! 3秒の遅延の後、2番目の「ON」パルスが開始され、その後も「ON」のままになります。

- さらに3秒の遅延の後、3番目の「ON」パルスが開始され、これも「ON」のままで、シーケンスは10個のLED(ソリッドステートリレー)がすべてオンになるまで続き、最終的に電源が「OFF」になるまで「ON」のままです。コンサートが終了し、オーディオラックの電源がオフになって、トラックにロードされた後。先に述べたように、駆動されるLEDは、実際には25アンペアのソリッドステートリレーの内部にあるLEDです。

- これらのソリッドステートリレーのAC負荷側は、アンプラックの背面に取り付けられるラックマウントシャーシの背面パネルにある米国標準の「壁コンセントプラグ」に配線されます。

- 回路には独自のDC電源が必要であることはすでに理解しており、この回路用のPCBと小さなAC / DC電源モジュールの設計を計画しています。電子メールで直接私に返信する場合は、これらのオーディオラックのいくつかを示す写真で返信することができます。

- 各ラックは10,000ワットのオーディオパワーを出力します!!!回路図とPCB設計には、AltiumまたはCADENCE / OrCADのいずれかを使用しています。上で詳述した要件を満たすように設計された回路図を私に提供できない場合は、おそらく私にできる人の名前を提供することができます。

- ただし、上記の記事を読んだように、タイミング回路の設計にはかなりの能力があるようです。ありがとう!!!

- 最後のコメント…..この回路は、非常に信頼性が高く、失敗しないでください。どのような種類の「オフ」の失敗でも、世界的に有名なアーティスト、バンド、および/または音楽家!!!

デザイン

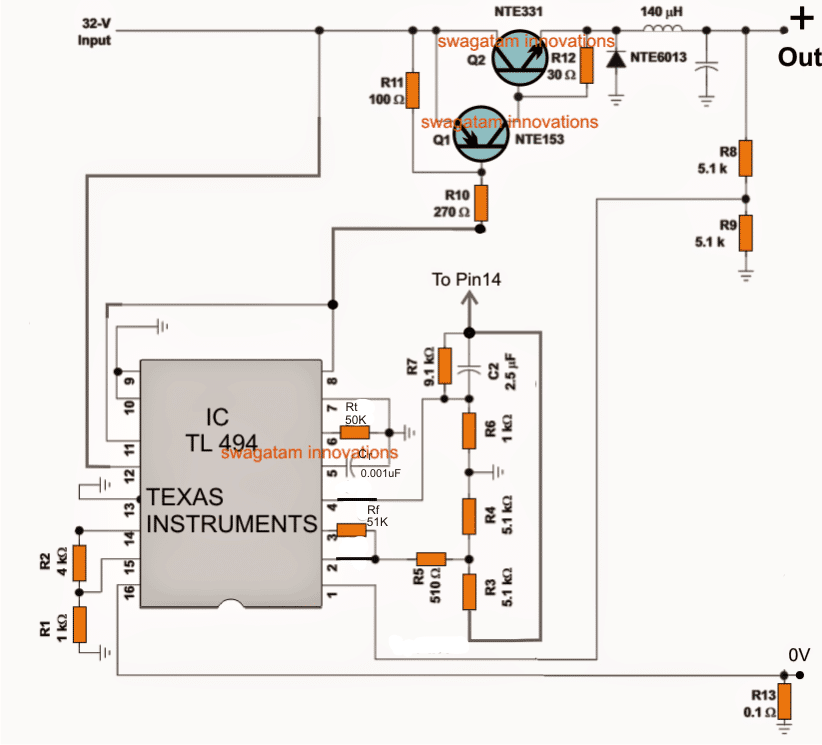

遅延が調整可能な10ステップシーケンシャルラッチスイッチ回路に要求される設計を以下の図に示します。これは、次の説明を参考にして理解できます。

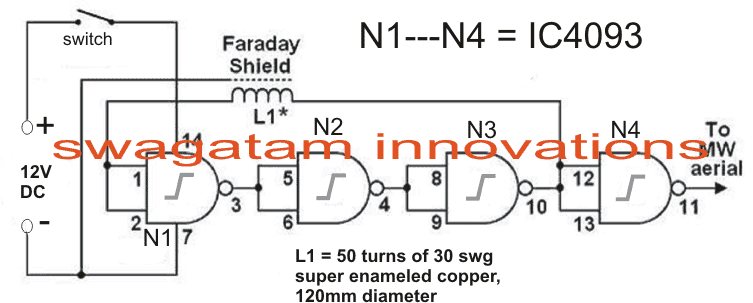

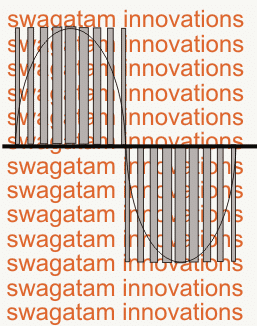

ここで採用されている回路設計は基本的に 標準のIC4017およびIC555ベースのチェイサー ここで、IC555は、IC4017のピン#14にクロックを送信し、その出力が、そのピン#3を横切って順次追跡出力を生成することを可能にする。

ピン#11。

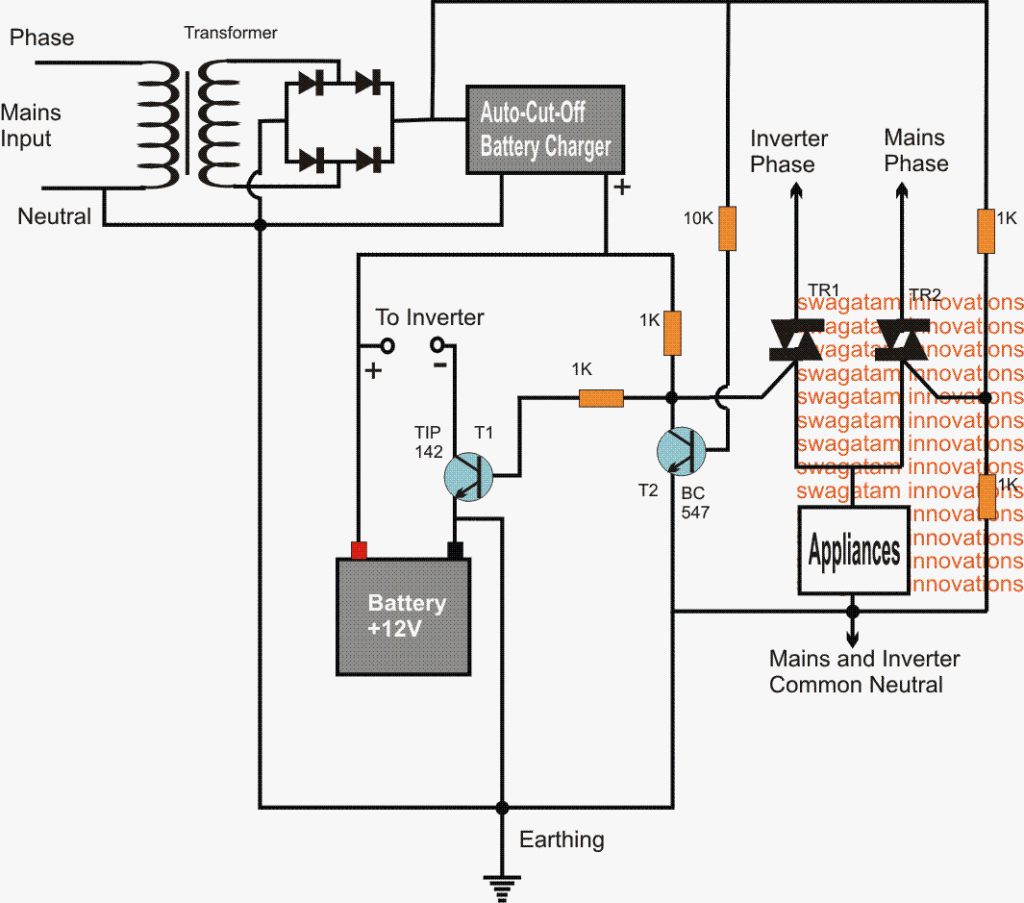

“三相から単相への配線 ”

ただし、の内部仕様に従って 10ステージのジョンソンディケードカウンターであるIC4017 、レジスタIC、ロジックが1つのピン配置から別のピン配置にジャンプすると、出力ピン配置全体でシーケンスロジックがハイになります。

シーケンスロジックがピン配置全体で確実にラッチされるようにするために、外部負荷をトリガーするためのSCRを導入します。 私たちが知っているSCRには、DCスイッチングにラッチされる特性があります ゲートへの単一のトリガーに応答して、このデバイスのこの特性を利用して、4017ピン配列からラッチされたシーケンス出力を取得します。

回路図

要求に応じて、10個の出力すべてがオンになるとシーケンスがフリーズする必要があります。これは、ICのピン#11をピン#13にリンクすることで実現します。これにより、ロジックが最後に達するとすぐにICがロックダウンします。順番にピン配置:ピン#11。

シーケンシングシフトの遅延時間は、IC555に関連付けられた100kポットを調整することで設定できます。

この回路は、アンプに適用される意図された10ステップのシーケンシャルスイッチングラッチ回路を満たしますが、柔軟性が高すぎる設計は、他の同様のアプリケーションのニーズに合わせてカスタマイズできます。

パーツリスト

すべてのSCRゲート抵抗:1K、1/4ワット

他のすべての抵抗器も1/4ワット定格にすることができます

すべてのSCRはBT169である可能性があり、前述のC106は適切ではないため、無視する必要があります。

SSRモジュールは、ユーザーの好みに応じて使用できます。

前:電気モーターの自動トルクオプティマイザー回路 次へ:BJTエミッタフォロワ–動作中、アプリケーション回路