IC 4040は、技術的には12段のバイナリリップルカウンタチップであり、簡単に言えば、クロック入力に印加されるすべてのパルスに応答して計算された遅延周波数出力を生成するデバイスです。この遅延は2 ^(n)の割合で増加します。ここで、nは出力シーケンスのピン配置順序です。

主な技術仕様

ICの主な機能と仕様は次のように理解できます。

入力クロックをレート2 ^(n)で分割する完全にバッファリングされた12個の出力。ここで、n = Q0からQ11までのピン配置順序。

上記の出力のシーケンスは、クロック入力CPピン配置で適用されるクロックのすべての立ち下がりエッジに応答して行われます。 ICは、比較的遅い立ち下がりクロックパルスにも同様に効果的に応答します。

ハイロジックが適用されるとすべての出力をゼロにリセットする単一の非同期マスターリセット(MR)入力。一方、一定のローロジックによりICはアクティブのままになります。

ICは3Vの低いVddで完全に動作可能になり、15V付近の電圧でも一定の動作特性を維持します。

IC4040で超えてはならないパラメータを調べてみましょう

- 供給電圧(Vdd)=通常3V〜15Vで、18Vが最大制限です。

- 入力電圧(Vi)= CP、MRなどの入力に印加できる電圧は、通常、Vdd未満、または最大で= Vdd + 0.5Vである必要があります。

- 非常に多くの出力が含まれ、各出力が含まれるため、最適な動作電流要件= 50mA

ピン配置の詳細

上の図は、IC 4040のピン配置構成を示しています。これらは、以下のように評価できます。

ピン配列Q0〜Q11はICの出力です。

“プルアップとプルダウン ”

- Vssはグランドピンです。

- Vddは正のピンです。

- MRはリセットピン配列です

- CPはクロック入力です。

タイミングシーケンス

次に、IC 4040の出力タイミングシーケンスを分析しましょう。次の図に示すように、次の詳細を確認して理解することができます。

MR入力がハイである限り、IC出力は応答を生成しません。ローになるとすぐに、ICは応答を開始し、CP入力で入力クロックをカウントします。

最初の出力ピンQ0は、CPで2 ^(n)クロック後にハイになります。つまり、= 2 ^(0)= 1です。つまり、Q0は最初のパルスの立ち下がりエッジでハイになり、の立ち下がりエッジに応答してローになります。後続の時計など。

同様に、Q1は2 ^(1)= 2の後にハイになります。つまり、2番目のクロックの立ち下がりエッジが検出されるとすぐにハイになり、次の4番目のクロックの立ち下がりエッジでローになります。

同様に、Q2は2 ^(2)= 4番目のクロックの立ち下がりエッジの後にハイとローになります。

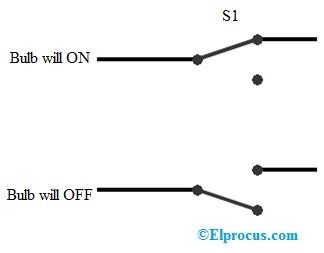

“双方向スイッチ接続図 ”

上記のシーケンスは、CPでの持続クロック入力に応答して、Q11まで続きます。

つまり、CPが1Hzのパルスでクロックされているとすると、Q11は2 ^ 11秒後または2048秒後にハイになります。これは約34分に相当します。クロック入力を増やすだけで達成できる遅延の範囲を想像してみてください。秒またはおそらく分単位で。

アプリケーションのヒント

IC 4040データシートの上記の詳細な分析から、ICは通常、周波数分割要件または遅延時間生成要件を含むすべてのアプリケーションに適していると結論付けることができます。

したがって、分周器回路アプリケーション、長時間タイマー、フラッシャー、およびその他の同様のアプリケーションに特に適したものになる可能性があります。

前:PCBの代わりにハイワットLEDにアルミニウムストリップヒートシンクを使用 次へ:洗濯機モーターアジテータータイマー回路