マルチバイブレータ回路は特別な 電子回路の種類 パルス信号の生成に使用されます。これらのパルス信号は、方形波信号または方形波信号にすることができます。これらは通常、高または低の2つの状態で出力を生成します。マルチバイブレータの特定の特性は、出力状態を決定するために抵抗やコンデンサなどのパッシブ要素を使用することです。

マルチバイブレータ回路

マルチバイブレーターの種類

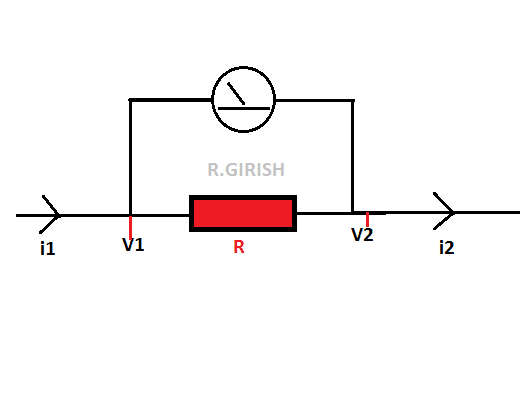

に。 単安定マルチバイブレータ :単安定マルチバイブレータは、出力が1つの安定状態のみにあるマルチバイブレータ回路のタイプです。ワンショットマルチバイブレータとも呼ばれます。単安定マルチバイブレータでは、出力パルス幅はRC時定数によって決定され、次のように与えられます。1.11* R * C

b。 安定したマルチバイブレータ :安定したバイブレータは、発振出力を備えた回路です。外部トリガーは必要なく、安定した状態もありません。回生発振器の一種です。

c。 双安定マルチバイブレータ :双安定バイブレータは、高と低の2つの安定状態を持つ回路です。通常、出力のハイ状態とロー状態を切り替えるにはスイッチが必要です。

3種類のマルチバイブレータ回路

1.トランジスタの使用

a。単安定マルチバイブレータ

単安定マルチバイブレータ回路

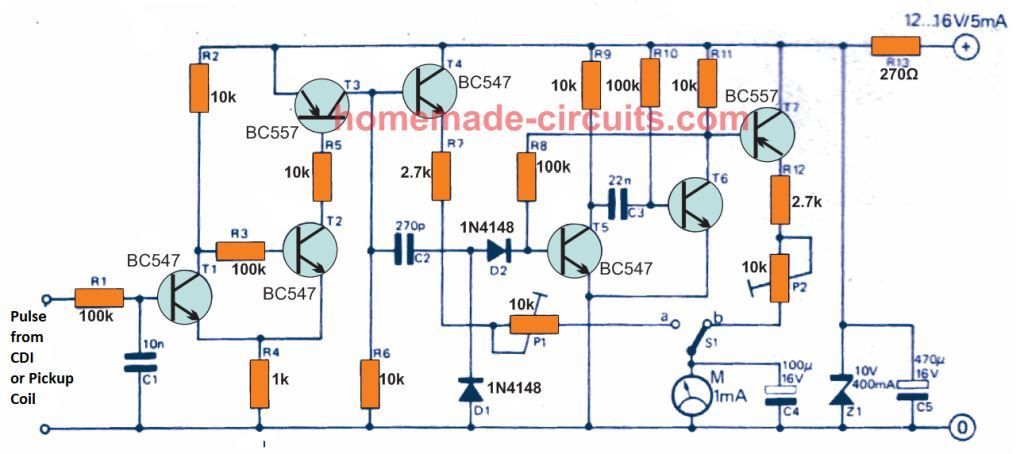

上記の回路では、外部トリガー信号がない場合、トランジスタT1のベースはグランドレベルにあり、コレクタはより高い電位にあります。したがって、トランジスタは遮断されます。ただし、トランジスタT2のベースは抵抗を介してVCCから正の電圧供給を受け、トランジスタT2は飽和状態に駆動されます。また、出力ピンはT2を介してグランドに接続されているため、ロジックローレベルになります。

トリガー信号がトランジスタT1のベースに印加されると、ベース電流が増加するにつれて導通を開始します。トランジスタが導通すると、そのコレクタ電圧は低下します。同時に、コンデンサC2の電圧がT1を介して放電を開始します。これにより、T2のベース端子の電位が低下し、最終的にT2が遮断されます。出力ピンは抵抗を介して正の電源に直接接続されているため、Voutはロジックハイレベルです。

しばらくして、コンデンサが完全に放電されると、抵抗を介して充電を開始します。トランジスタT2のベース端子の電位は徐々に上昇し始め、最終的にT2は導通状態になります。したがって、出力は再び論理ローレベルになるか、回路は安定状態に戻ります。

b。双安定マルチバイブレータ

双安定マルチバイブレータ回路

上記の回路は、回路の2つの安定状態を定義する、2つの出力を備えた双安定マルチバイブレータ回路です。

最初、スイッチが位置Aにあるとき、トランジスタT1のベースは接地電位にあるので、それは遮断される。同時に、トランジスタT2のベースは比較的高い電位にあり、導通を開始します。これにより、出力ピン1が直接グランドに接続され、Vout1がロジックローレベルになります。 T1のコレクタの出力ピン2はVccに直接接続されており、Vout2はロジックハイレベルです。

ここで、スイッチが位置Bにあるとき、トランジスタの動作が逆になり(T1が導通し、T2が遮断されます)、出力状態が逆になります。

c。 Astableマルチバイブレータ

非安定マルチバイブレータ回路

上記の回路は発振回路です。最初にトランジスタT1が導通状態にあり、T2が遮断されていると仮定します。出力2はロジックレベルで、出力1はロジックローレベルです。コンデンサc2がR4を介して充電を開始すると、T2のベースの電位は、T2が導通を開始するまで徐々に増加し始めます。これによりコレクタ電位が低下し、T1の基部の電位が徐々に低下し始め、完全に遮断されます。

ここで、C1がR1を介して充電されると、トランジスタT1のベースの電位が上昇し始め、最終的には導通状態になり、プロセス全体が繰り返されます。したがって、出力は常に繰り返しまたは振動しています。

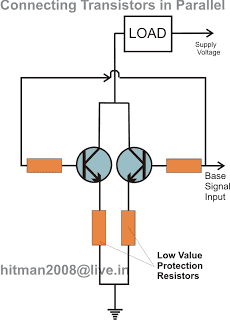

BJTの使用とは別に、その他 トランジスタの種類 マルチバイブレータ回路でも使用されます。

2.論理ゲートの使用

に。単安定マルチバイブレータ

単安定マルチバイブレータ回路

最初、抵抗の両端の電位はグランドレベルです。これは、NOTゲートの入力への論理信号が低いことを意味します。したがって、出力はロジックハイレベルになります。

NANDゲートの両方の入力が論理ハイレベルであるため、出力は論理ローレベルであり、回路出力は安定した状態のままです。

ここで、NANDゲートの入力の1つに論理ロー信号が与えられ、もう1つの入力が論理ハイレベルであるとすると、ゲートの出力は論理1、つまり正の電圧になります。 Rの両端に電位差があるため、VR1はロジックハイレベルであり、したがってNOTゲートの出力はロジック0です。このロジックロー信号はNANDゲートの入力にフィードバックされるため、その出力はロジック1のままであり、コンデンサの電圧は徐々に上昇し始めます。これにより、抵抗の両端の電位降下が発生します。つまり、VR1は徐々に減少し始め、ある時点でローになり、論理ロー信号がNOTゲートの入力に供給され、出力は再びロジックハイ信号になります。出力が安定状態に留まる期間は、RC時定数によって決まります。

b。 Astableマルチバイブレータ

非安定マルチバイブレータ回路

最初に、電源が供給されると、コンデンサは充電されず、論理ロー信号がNOTゲートの入力に供給されます。これにより、出力はロジックハイレベルになります。このロジックハイ信号がANDゲートにフィードバックされると、その出力はロジック1になります。コンデンサは充電を開始し、NOTゲートの入力レベルは、ロジックハイしきい値に達するまで増加し、出力はロジックローになります。

この場合も、ANDゲート出力はロジックローになり(ロジックロー入力がフィードバックされます)、コンデンサはNOTゲートの入力の電位がロジックローしきい値に達するまで放電を開始し、出力は再びロジックハイに戻ります。 。

これは実際には一種の 弛張発振回路 。

c。双安定マルチバイブレータ

双安定マルチバイブレータの最も単純な形式は、論理ゲートによって実現されるSRラッチです。

双安定マルチバイブレータ回路

初期出力がロジックハイレベル(Set)にあり、入力トリガー信号がロジックLow信号(Reset)にあるとします。これにより、NANDゲート1の出力が論理ハイレベルになります。 U2の両方の入力がロジックハイレベルであるため、出力はロジックローレベルです。

U3の両方の入力がロジックハイレベルであるため、出力はロジックローレベル、つまりリセットになります。入力のロジックハイ信号に対しても同じ動作が発生し、回路の状態が0と1の間で変化します。見られるように、マルチバイブレータのロジックゲートの使用は、実際にはデジタルロジック回路の例です。

3.555タイマーの使用

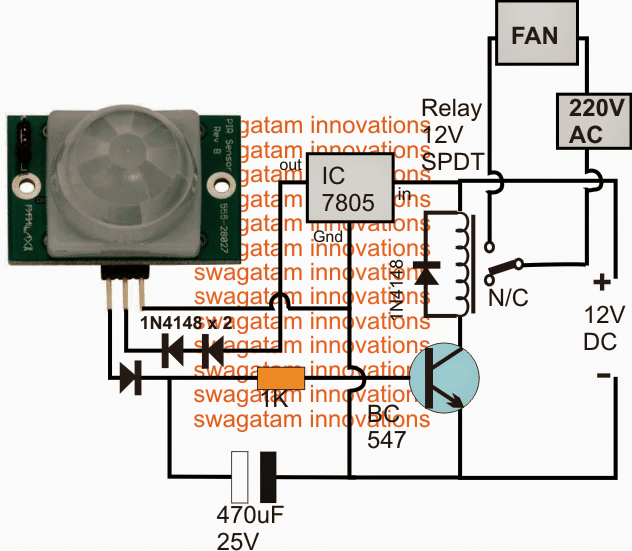

555タイマーIC 特にパルス生成に最も一般的に使用されるICです パルス幅変調 、マルチバイブレータ回路用。

a。単安定マルチバイブレータ

単安定マルチバイブレータ回路

単安定モードで555タイマーを接続するには、放電コンデンサを放電ピン7とグランドの間に接続します。生成される出力のパルス幅は、放電ピンVccとコンデンサCの間の抵抗Rの値によって決まります。

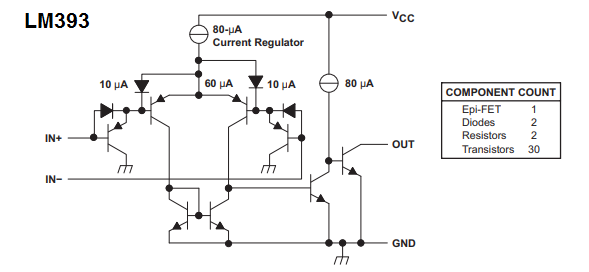

555タイマーの内部回路を知っている場合は、次の事実を知っている必要があります。 555タイマーが動作します トランジスタ、2つのコンパレータ、SRフリップフロップを備えています。

最初に、出力がロジックロー信号のとき、トランジスタTは導通状態に駆動され、ピン7は接地されます。この電圧が1 / 3Vcc未満であるため、ロジックロー信号がトリガ入力またはコンパレータの入力に印加されたとすると、コンパレータICの出力がハイになり、フリップフロップがリセットされて出力がロジックローレベルで。

同時に、トランジスタがオフになり、コンデンサはVccを介して充電を開始します。コンデンサの電圧が2 / 3Vccを超えると、コンパレータ2の出力がハイになり、SRフリップフロップがセットされます。したがって、出力は、RとCの値によって決定される特定の期間の後、再び安定状態になります。

b。 Astableマルチバイブレータ

555タイマーを非安定モードで接続するには、ピン2と6を短くし、ピン6と7の間に抵抗を接続します。

非安定マルチバイブレータ回路

最初に、SRフリップフロップの出力がロジックローレベルであると仮定します。これによりトランジスタがオフになり、コンデンサはRaとRbを介してVccへの充電を開始し、コンパレータ2への入力電圧がしきい値電圧の2 / 3Vccを超え、コンパレータ出力がハイになります。これにより、SRフリップフロップは、タイマー出力がロジックローになるように設定されます。

ここで、トランジスタはそのベースでロジックハイ信号によって飽和状態に駆動されます。コンデンサはRbを介して放電を開始し、このコンデンサ電圧が1/3 Vccを下回ると、コンパレータC2の出力は論理ハイレベルになります。これによりフリップフロップがリセットされ、タイマー出力は再びロジックハイレベルになります。

c。双安定マルチバイブレータ

双安定マルチバイブレータ回路

双安定マルチバイブレータの555タイマーは、コンデンサを使用する必要はなく、グランドとピン2および4の間にSPDTスイッチが使用されます。

スイッチの位置がピン2がピン6とともにグランドにあるようになっている場合、コンパレータ1の出力は論理Low信号になり、コンパレータ2の出力は論理High信号になります。これによりSRフリップフロップがリセットされ、フリップフロップの出力はロジックローになります。したがって、タイマーの出力はロジックハイ信号です。

スイッチの位置がフリップフロップのピン4またはリセットピンが接地されるようになっている場合、SRフリップフロップがセットされ、出力はロジックハイになります。タイマーの出力はロジックロー信号です。したがって、スイッチの位置に応じて、高パルスと低パルスが得られます。

したがって、これらはパルス生成に使用される基本的なマルチバイブレータ回路です。マルチバイブレーターについてご理解いただければ幸いです。

これがすべての読者への簡単な質問です:

マルチバイブレータとは別に、パルス生成に使用される他のタイプの回路は何ですか?