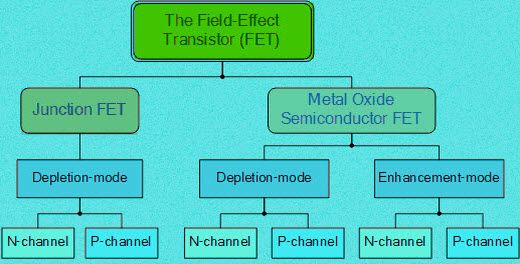

以前、の設計 論理回路 を使用して行うことができます SSI(小規模統合) 論理ゲートなどのコンポーネント、 マルチプレクサ 、デマルチプレクサ、FFなど。ただし、PLDでこれらすべてのSSIコンポーネントを置き換えることができるようになりました。したがって、これがPLDと比較してSSI業界を減少させる理由であり、これらはいくつかのアプリケーションで使用されています。ザ・ プログラマブルロジックデバイスまたはPLD 論理回路を実装するために使用されるチップの一種です。これには、いくつかの方法で変更できる論理回路要素のセットが含まれています。 PLDは、プログラマブルスイッチと論理ゲートで構成されるブラックボックスのように見えます。スイッチの主な機能は、PLD内の論理ゲートを相互に関連付けて論理回路を実行できるようにすることです。 PLDは、SPLD-simple PLD( PLA&PAL )、 CPLD-コンプレックスPLD 、 FPGA- フィールドプログラマブルゲートアレイ 。この記事では、PALとPLAとは何か、設計とそれらの違いについて説明します。

PALとPLAとは何ですか?

両方とも プログラマブルアレイロジック そして プログラマブルロジックアレイ はPLD(プログラマブルロジックデバイス)の一種で、主にシーケンシャルロジックで相互にコンビネーションロジックを設計するために使用されます。これら2つの主な違いは、PALはANDゲートのコレクションとORゲートの固定コレクションを使用して設計できるのに対し、PLAはORゲートの固定コレクションを使用してANDのプログラマブルアレイを使用して設計できることです。プログラマブルロジックデバイスは、シンプルで柔軟なロジック回路設計を提供します。

プログラマブルアレイロジック

プログラマブルロジックデバイスの前は、 組み合わせ論理回路 マルチプレクサを使用して設計することができ、これらの回路は複合であると同時に剛性が高いため、PLDが開発されます。最初のプログラマブルロジックデバイスはROMでしたが、ハードウェアの浪費の問題と、すべてのハードウェアアプリケーションでの指数関数的成長の強化により、成功しませんでした。この問題を克服するために、PALとPLAが使用されました。これら2つはプログラム可能であり、ハードウェアを効率的に使用します。

プログラマブルロジックアレイ

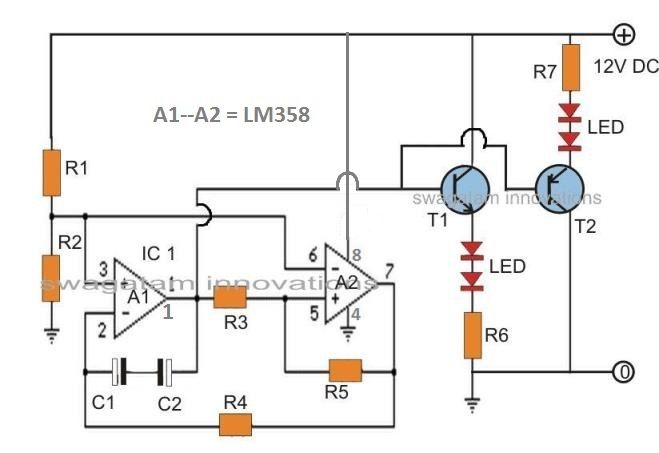

プログラマブルアレイロジック(PAL)の設計

ザ・ 用語PALまたはプログラマブルアレイロジックの定義 はプログラマブルロジックデバイス回路として知られているPLDの一種であり、このPALの動作はPLAと同じです。プログラマブルアレイロジックの設計は、固定ORゲートとプログラマブルANDゲートを使用して行うことができます。これを使用することにより、各ORゲートに関連付けられたANDゲートが、次の形式で生成できる製品条件の最大数を示す場合に、2つの簡単な関数を実装できます。 SOP(製品の合計) 正確な関数の。

ANDのような論理ゲートはORゲートに向かって継続的に接続されているため、生成された積項が出力関数に分散されていないことを示しています。 PLD開発の背後にある主な概念は、欠陥のある配線を取り除き、ロジック設計を回避し、電力消費を削減することにより、複合ブールロジックを単一チップ上に製造することです。

PALの例

以下を実装します ブール式 の助けを借りて プログラマブルアレイロジック(PAL)

X = AB + AC '

Y = AB ’+ BC’

上記の2つ ブール関数 の形である SOP(製品の合計) 。ブール式に存在する積項はXとYであり、AC ’である1つの積項はすべての方程式で共通です。したがって、上記の2つの式を生成するために必要な論理ゲートの合計は、ANDゲート-4またはプログラム可能なゲート-2です。同等のPALロジック図を以下に示します。

PAL論理回路

プログラム可能なANDゲートには、通常の可変入力と補完された可変入力の入力権があります。上記の論理図では、各ANDゲートで使用可能な入力はA、A '、B、B'、C、C 'です。したがって、すべてのANDゲートで単一の積項を生成するには、プログラムが必要です。

すべての積項は、各ORゲートの入力で取得できます。ここで、論理ゲートのプログラム可能な接続は、記号「X」で表すことができます。

ここでは、ORゲート入力が固定されています。したがって、必要な積項は各ORゲート入力に関連付けられています。その結果、これらのゲートは特定のブール方程式を生成します。ザ・ '。' 記号は永続的な接続を表します。

プログラマブルロジックアレイ(PLA)の設計

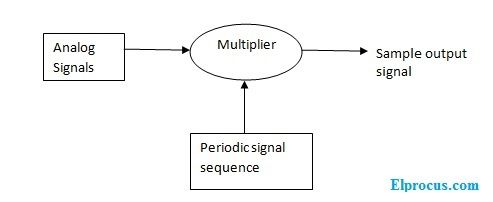

PLAという用語の定義は、ブール関数を積の合計(SOP)の形式で表します。このプログラマブルロジックアレイの設計は、AND、ORなどの論理ゲートを使用して行うことができます。チップ上に製造することにより、すべての入力とその補数をすべてのANDゲートに対して取得できます。

すべてのANDゲートの出力は、すべてのORゲートに接続されます。最後に、ORゲートの出力がチップの出力を生成します。したがって、これは、積の合計の式を使用するための適切な関連付けが完了する方法です。プログラマブルロジックアレイでは、AND&ORなどの論理ゲートの接続をプログラムできます。 PLAは高価であり、PALと比較するのは困難です。 PALは、プログラミングの楽さを向上させるためのプログラマブルロジックアレイに使用できる、2つの異なる開発された方法を使用します。この種の方法では、すべての接続は、ヒューズの溶断によって不要な接続を切り離すことができる場所であればどこでも、各交点でヒューズを使用して行うことができます。最終的な技術は、正確な相互接続モデルに提供される適切なカバーを使用した製造プロセス中に接続の作成を行います。

“交流を使うもの ”

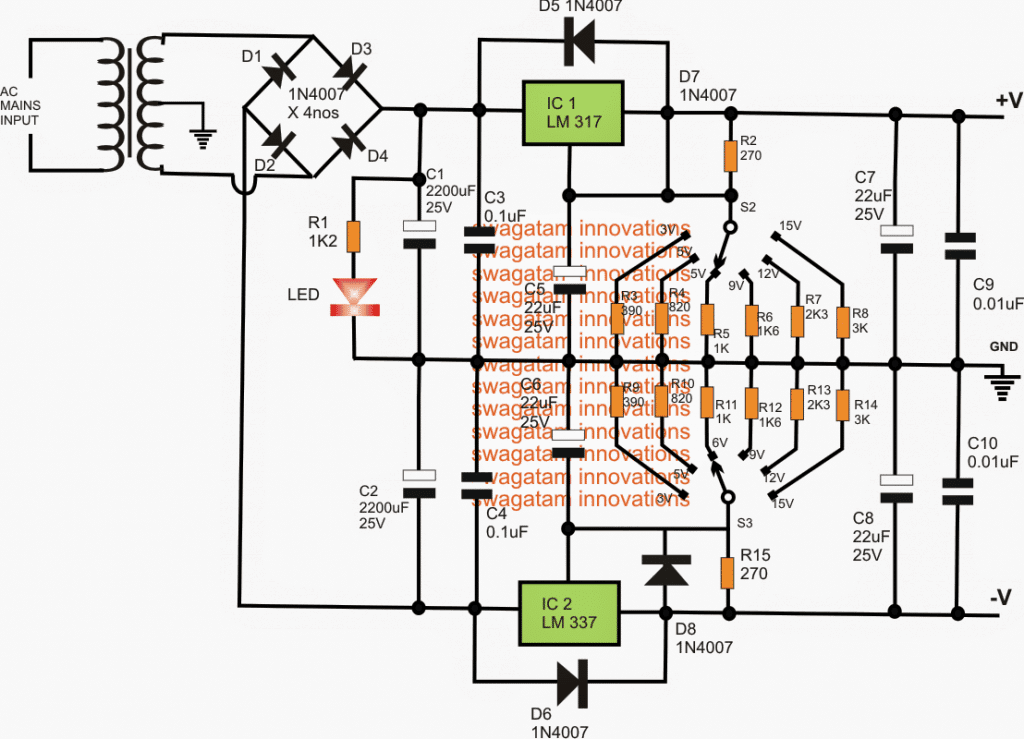

PLAの例

プログラマブルロジックアレイ(PLA)を使用して、次のブール式を実装します。

X = AB + AC '

Y = AB '+ BC + AC'

上記の2つのブール関数は、SOP(積の合計)の形式です。ブール式に存在する積項はXとYであり、AC ’である1つの積項はすべての方程式で共通です。したがって、上記の2つの式を生成するために必要な論理ゲートの合計は、ANDゲート-4、ORプログラム可能なORゲート-2です。同等のPLA論理図を以下に示します。

PLA論理回路

プログラム可能なANDゲートには、通常の可変入力と補完された可変入力の入力権があります。上記の論理図では、各ANDゲートで使用可能な入力はA、A '、B、B'、C、C 'です。したがって、すべてのANDゲートで単一の積項を生成するには、プログラムが必要です。

すべての積項は、各ORゲートの入力で取得できます。ここで、論理ゲートのプログラム可能な接続は、記号「X」で表すことができます。

PALとPLAの違い

ザ・ 表形式のPALとPLAの違い 主に含まれています PALおよびPLAフルフォーム 、構造、可用性、柔軟性、コスト、機能の数、および速度については、以下で説明します。

| プログラマブルアレイロジック(PAL) | プログラマブルロジックアレイ(PLA) |

| PALの完全な形式はプログラマブルアレイロジックです | PLAの完全な形式は、プログラマブルロジックアレイです。 |

| PALの構築は、プログラム可能なANDおよびORゲートのコレクションを使用して実行できます。 | PLAの構築は、ANDのプログラム可能なコレクションとORゲートの固定コレクションを使用して行うことができます。 |

| PALの可用性はそれほど多くありません | PLAの可用性はもっと |

| PALプログラミングの柔軟性はさらに高い | PLAの柔軟性は低い |

| PALのコストは高いです | PLAのコストは中程度です |

| PALに実装されている機能の数が多い | PLAに実装されている機能の数は限られています |

| PALの速度が遅い | PLAの速度は速い |

したがって、これはすべてPALとPLAに関するものです。上記の情報から、最後に、これらはプログラマブルロジックデバイス(PLD)であると結論付けることができます。 プログラマブルロジックアレイ プログラマブルアレイロジックよりも柔軟性があります。しかし、プログラマブルアレイロジックは、組み合わせロジック回路を簡単に生成できます。ここにあなたへの質問があります、の役割は何ですか デジタルエレクトロニクスにおけるPALとPLA ?