ここでは、入力トリガーが解放された後にのみ出力単安定持続時間が開始する単純なIC 555ベースの単安定回路を研究します。したがって、トリガーON持続時間は、単安定の事前にプログラムされたON持続時間に追加されます。アイデアはジョン・ブローガン氏からリクエストされました

技術仕様

非常に簡単なプロジェクトにあなたを雇うことができるかどうか知りたいのですが。これは私が回路を学ぶのを助けるためです。

次のタイプの回路を探しています(以下を参照)。設計にかかる費用を教えてください。

回路基板には4つのピンがあります。ボードの左側に2つのピン、右側に2つのピン。

誰かがボードの左側の回路を瞬間的に、またはどれだけ長く閉じたままにしておくと、ボードの右側のピンは、左側の回路の2分後に* PLUS *を閉じます。ボードのが開かれます。 (それは私が立ち往生している部分です-別の回路が開かれた時間を過ぎて「n」分間回路を閉じたままにする方法。

これを図解するために請求する金額と、これを作成するために購入する必要のある部品をリストしてください。

ありがとうございました!

ジョン・ブローガン

コロラド

デザイン

言い換えると、上記の要求は、入力トリガーが解放されたときにのみ状態遅延の出力が開始される単安定を要求します。つまり、単安定が2分の遅延を生成するように設計されていると仮定し、入力トリガーの保持時間をxと仮定します。分、ICの出力ピン3での合計遅延は= 2分+ 'x'分である必要があります。

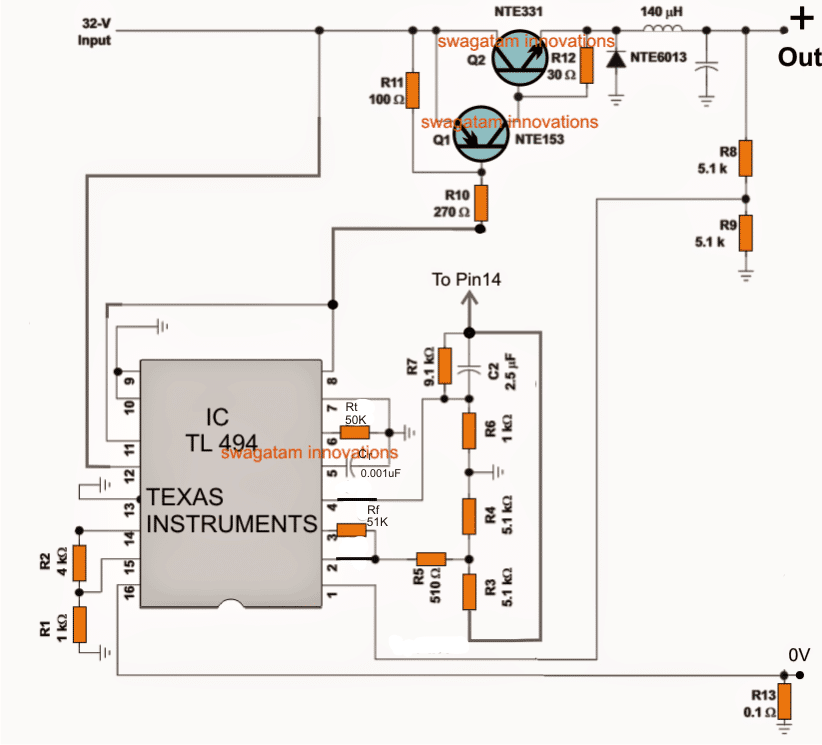

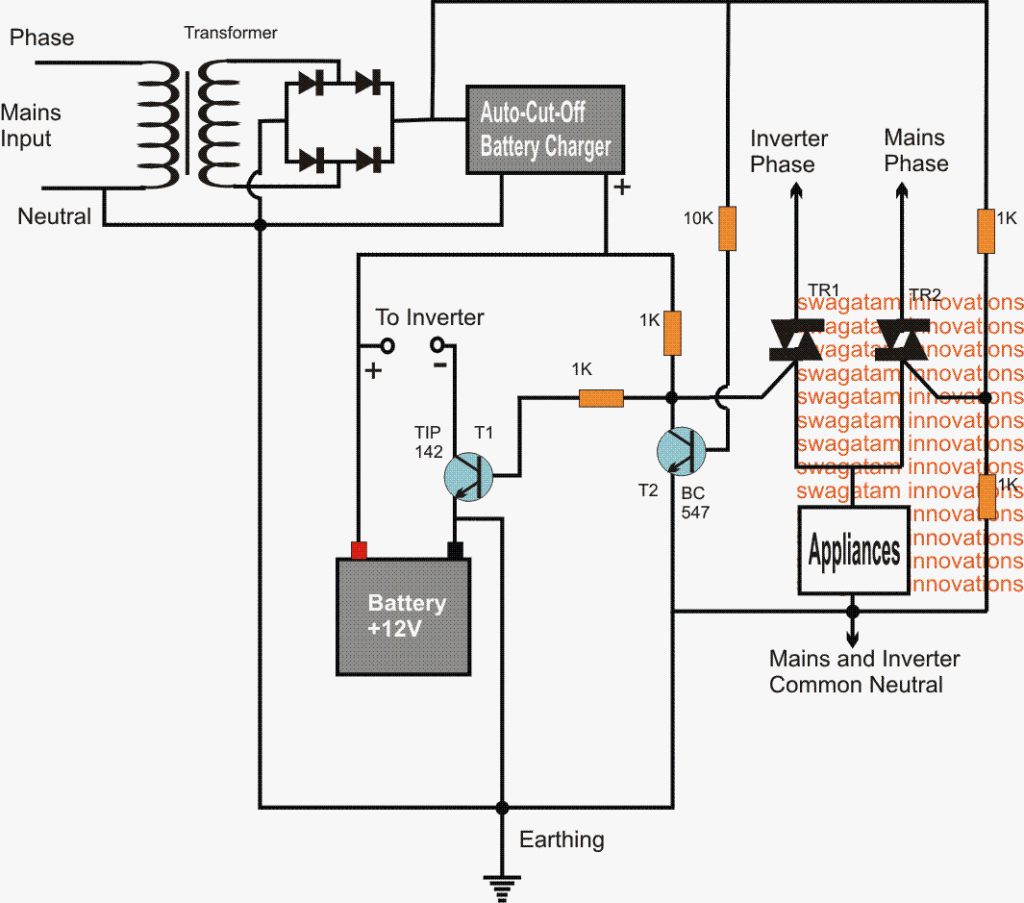

設計は、標準のIC555単安定回路にPNPステージを追加することで簡単に構成できます。

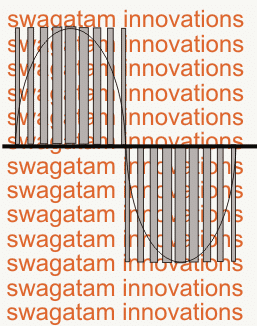

下の図を参照すると、R2とC1によって決定される時間遅延に対してHighの出力を生成する標準のIC555単安定回路がわかります。これは、pin2が瞬間的に接地されるたびに、または比較的長い時間接地されるたびに開始されます。

ただし、通常、これはトリガーのオン期間を考慮せずにピン2が接地されるとすぐに発生するため、提案された設計ではこの状況は望ましくありません。

この問題は、回路の示されている位置全体にPNPデバイスT1を含めることで効果的に解決されます。

左側のピンが閉じているときの要求で示唆されているように、T1は負のバイアスで許可され、強制的に導通させます。

上記の条件では、出力はハイになりますが、T1エミッタ/コンデンサを介してタイミングコンデンサC1が短絡するため、ユーザーが左側のピンを開くまで充電できません。

左側のピンが解放されると、C1は充電され、単安定カウント操作を開始します。この動作では、リレーが作動して、設定された合計2分間と入力が閉じられた時間の合計で右側のピンを閉じます。

回路図

IC555ピン配置仕様

前:オーディオパワーアンプ用SMPS 2 x 50V 350W回路 次へ:デュアルA / Cリレー切り替え回路