ユニジャンクショントランジスタは、BJTとは異なりpn接合が1つしかない3端子半導体デバイスです。基本的には、デジタル回路アプリケーションに適したパルス信号を生成するための単段発振回路として使用するように設計されています。

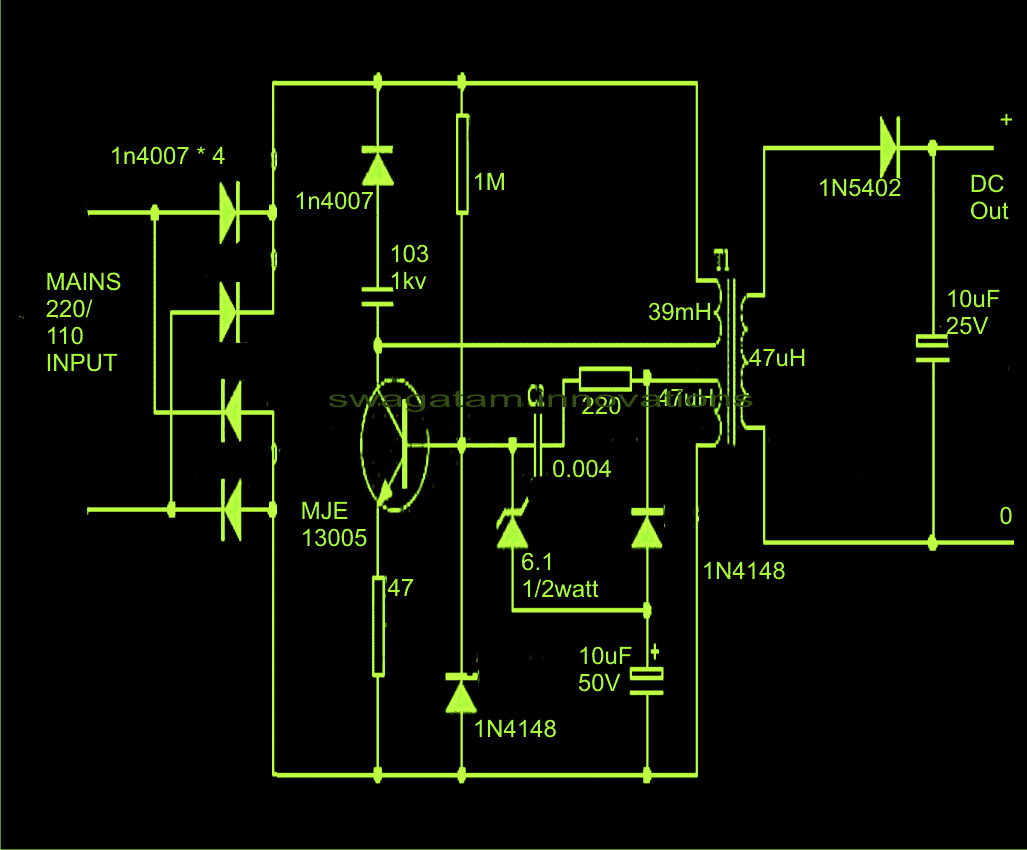

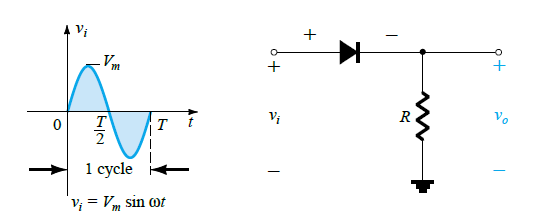

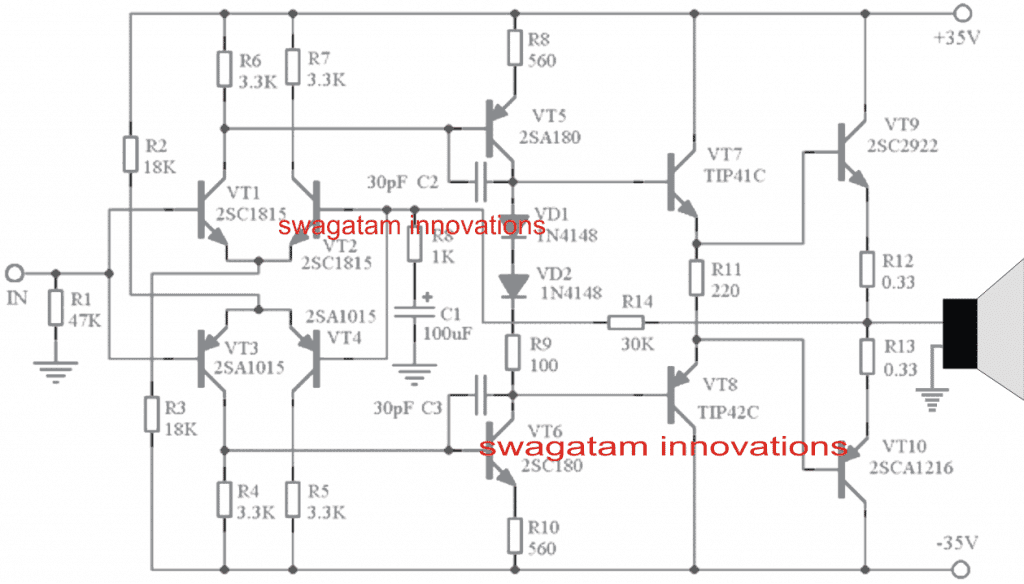

UJT弛緩発振器回路

ユニジャンクショントランジスタは、通常、次の基本回路に示すように、緩和発振器の形で配線できます。

ここで、コンポーネントRTおよびCTはタイミング要素のように機能し、UJT回路の周波数または発振速度を決定します。

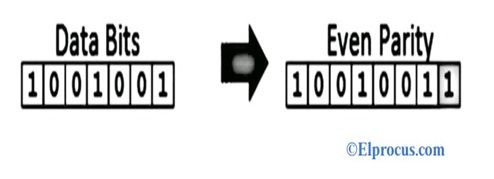

発振周波数の計算には、次の式を使用できます。 ユニジャンクショントランジスタ固有のスタンドオフ比 インクルード 振動パルスを決定するためのRTおよびCTとともにパラメータの1つとして。

一般的なUJTデバイスのスタンドオフ比の標準値は0.4〜0.6です。 。したがって、 インクルード = 0.5であり、上記の式に代入すると、次のようになります。

電源がオンになると、抵抗RTを介した電圧により、コンデンサCTが電源レベルVBBに向かって充電されます。ここで、スタンドオフ電圧Vpは、UJTスタンドオフ比と組み合わせて、B1-B2の両端のVpによって決定されます。 インクルード として:Vp = インクルード VB1VB2-VD。

コンデンサ両端の電圧VEがVpよりも低いままである限り、B1、B2の両端のUJT端子は開回路を示します。

しかし、CTの両端の電圧がVpを超えると、ユニジャンクショントランジスタが起動し、コンデンサが急速に放電され、新しいサイクルが開始されます。

UJTの起動インスタンス中に、R1全体の電位が上昇し、R2全体の電位が低下します。

UJTのエミッタを横切る結果の波形は、のこぎり波信号を生成します。これは、UJTのB2リードで正方向の電位を示し、B1リードで負方向の電位を示します。

ユニジャンクショントランジスタの応用分野

以下は、ユニジャンクショントランジスタが広く使用されている主なアプリケーション分野です。

- トリガー回路

- 発振器回路

- 電圧/電流調整電源。

- タイマーベースの回路、

- 鋸歯状発電機、

- 位相制御回路

- 双安定ネットワーク

主な特徴

簡単にアクセスできて安い :UJTの安価で入手しやすいことと、いくつかの優れた機能により、このデバイスは多くの電子アプリケーションに幅広く実装されています。

低消費電力 :通常の動作条件下での低消費電力機能により、このデバイスは、適度に効率的なデバイスを開発するための絶え間ない努力において、信じられないほどのブレークスルーと見なされています。

安定性の高い信頼性の高い操作 :オシレーターまたは遅延トリガー回路として使用する場合、UJTは非常に信頼性が高く、非常に正確な出力応答で動作します。

ユニジャンクショントランジスタの基本構造

図1

UJTは、上図のようなシンプルな構造の3端子半導体デバイスです。

この構造では、低濃度にドープされたn型シリコン材料のブロック(抵抗特性が向上)が、一方の表面の両端に接続された1対のベース接点と、反対側の背面に合金化されたアルミニウムロッドを提供します。

デバイスのp-n接合は、アルミニウムロッドとn型シリコンブロックの境界に作成されます。

このように形成された単一のp-n接合が、デバイスの名前の理由です「ユニジャンクション」 。このデバイスは当初、 デュオ(ダブル)ベースダイオード 一対のベース接点が発生したためです。

上の図では、アルミニウムロッドがベース1接点よりもベース2接点に近い位置でシリコンブロックに融合/マージされており、ベース2端子もベース1端子に対して正になっていることに注意してください。 VBBボルトで。これらの側面がUJTの動作にどのように影響するかは、次のセクションで明らかになります。

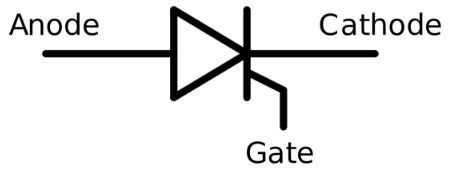

シンボリック表現

ユニジャンクショントランジスタの象徴的な表現は、下の画像で見ることができます。

図#2

エミッタ端子が、n型材料のブロックを表す直線に対して角度を付けて示されていることに注意してください。ユニジャンクションデバイスが順方向にバイアスされた状態、トリガーされた状態、または導通状態にあるときに、矢印の頭が通常の電流(正孔)の流れの方向を向いていることがわかります。

ユニジャンクショントランジスタの等価回路

図#3

同等のUJT回路は上の画像で見ることができます。この等価回路は、2つの抵抗(1つは固定、もう1つは調整可能)と1つのダイオードを含む比較的単純に見えることがわかります。

抵抗RB1は、現在のIEの変化に応じて値が変化することを考慮して、調整可能な抵抗として表示されます。実際、ユニジャンクションを表すトランジスタでは、IEが0から50 =μAに同等に変化すると、RB1は5kΩから50Ωまで変動する可能性があります。ベース間抵抗RBBは、IE = 0の場合の端子B1とB2の間のデバイスの抵抗を表します。これの式では、

RBB =(RB1 + RB2)| IE = 0

RBBの範囲は通常4〜10k以内です。最初の図に示すアルミニウムロッドの配置は、IE = 0の場合のRB1、RB2の相対的な大きさを提供します。以下に示すように、分圧器の法則を使用してVRB1の値(IE = 0の場合)を推定できます。

VRB1 =(RB1 x VBB)/(RB1 + RB2)=ηVBB(IE = 0の場合)

ギリシャ文字 インクルード (eta)は、ユニジャンクショントランジスタデバイスの固有のスタンドオフ比として知られており、次のように定義されます。

η= RB1 /(RB1 + RB2)(IE = 0の場合)= RB1 / RBB

ダイオードの順方向電圧降下VD(0.35→0.70 V)によってVRB1(=ηVBB)よりも高い指示されたエミッタ電圧(VE)の場合、ダイオードはオンにトリガーされます。理想的には、IEがRB1を介して導通を開始するような短絡状態を想定することができます。式により、エミッタのトリガー電圧レベルは次のように表すことができます。

VP =ηVBB+ VD

主な特徴と働き

VBB = 10Vの代表的なユニジャンクショントランジスタの特性を下図に示します。

図4

ピークポイントの左側に示されているエミッター電位の場合、IE値がIEO(マイクロアンペア単位)を超えることはないことがわかります。電流IEOは、従来のバイポーラトランジスタの逆リーク電流ICOにほぼ従います。

この領域は、図に示されているように、カットオフ領域と呼ばれます。

VE = VPで導通が達成されるとすぐに、IE電位が増加するにつれてエミッタ電位VEが減少します。これは、前述のように、電流IEを増加させるための抵抗RB1の減少と正確に一致します。

上記の特性により、非常に安定した負性抵抗領域を備えたユニジャンクショントランジスタが提供され、デバイスが動作し、非常に高い信頼性で適用できるようになります。

上記のプロセスの間に、最終的に谷点に到達することが期待でき、この範囲を超えてIEが増加すると、デバイスは飽和領域に入ります。

図3は、同じ領域にあるダイオードの等価回路を示しています。

活性領域でのデバイスの抵抗値の低下は、デバイスの発火が発生するとすぐに、p型アルミニウムロッドによってn型ブロックに注入された正孔のために引き起こされます。これにより、n型セクションの正孔の量が増加し、自由電子数が増加し、デバイス全体の導電率(G)が向上し、抵抗が同等に減少します(R↓= 1 / G↑)

重要なパラメータ

ユニジャンクショントランジスタに関連する3つの追加の重要なパラメータ、IP、VV、およびIVがあります。これらはすべて図4に示されています。

これらは実際には非常に理解しやすいです。通常存在するエミッタ特性は、図5の下から学ぶことができます。

図#5

ここでは、水平スケールがミリアンペアで校正されているため、IEO(μA)が目立たないことがわかります。縦軸と交差する各曲線は、VPの対応する結果です。 ηとVDの定数値の場合、VP値は、次のようにVBBに従って変化します。

ユニジャンクショントランジスタデータシート

UJTの技術仕様の標準範囲は、以下の図5から学ぶことができます。

UJTピン配列の詳細

ピン配置の詳細は、上記のデータシートにも含まれています。ベース端子に注意してください B1 そして B2 エミッタピンが互いに反対側にある間 IS これら2つの間の中央に配置されます。

さらに、より高い供給レベルで接続されることになっているベースピンは、パッケージのカラーのオフシュートの近くに配置されています。

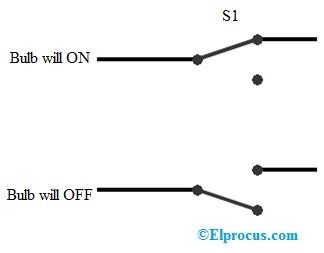

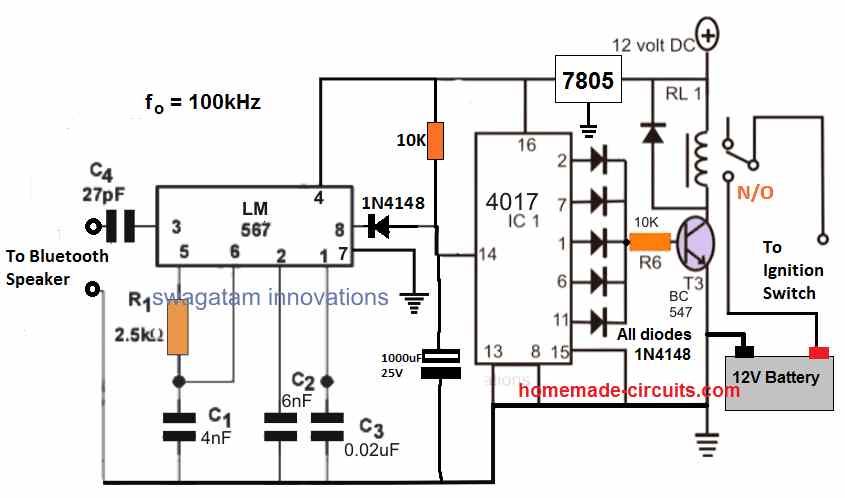

SCRをトリガーするためにUJTを使用する方法

UJTの比較的人気のあるアプリケーションの1つは、SCRなどのパワーデバイスをトリガーするためのものです。このタイプのトリガー回路の基本的なコンポーネントは、以下の図#6に示されています。

図6:UJTを使用したSCRのトリガー

図7:SCRなどの外部デバイスのトリガー用のUJT負荷線

主なタイミングコンポーネントはR1とCで構成され、R2は出力トリガー電圧のプルダウン抵抗のように機能します。

R1の計算方法

抵抗R1は、R1で定義された負荷線が負性抵抗領域内でデバイスの特性を介して移動することを保証するように計算する必要があります。つまり、ピークポイントの右側に向かって、バレーポイントの左側に向かって移動します。図7。

負荷線がピークポイントの右側を横切ることができない場合、ユニジャンクションデバイスは起動できません。

スイッチのオン状態を保証するR1の式は、IR1 = IPおよびVE = VPであるピークポイントを考慮に入れると決定できます。この時点でのコンデンサの充電電流はゼロであるため、式IR1 = IPは論理的に見えます。つまり、この特定のポイントのコンデンサは、充電を経て放電状態に移行しています。

したがって、上記の条件については、次のように書くことができます。

または、完全なSCRを確実にオフにするために:

R1>(V-Vv)/ Iv

これは、抵抗R1の選択範囲が次のように表される必要があることを意味します。

(V-Vv)/ Iv

R2の計算方法

IE≅0アンペアのときにR2の両端の電圧VR2によってSCRが誤ってトリガーされないように、抵抗R2は十分に小さくする必要があります。このため、VR2は次の式に従って計算する必要があります。

VR2≅R2V/(R2 + RBB)(IE≅0の場合)

コンデンサは、トリガーパルス間の時間遅延を提供し、各パルスの長さも決定します。

Cの計算方法

下の図を参照すると、回路に電力が供給されるとすぐに、VCに等しい電圧VEが、時定数τ= R1Cを介してコンデンサを電圧VVに向けて充電し始めます。

図#8

UJTネットワークでのCの充電期間を決定する一般式は次のとおりです。

vc = Vv +(V-Vv)(1- です-t / R1C)

以前の計算を通じて、コンデンサの上記の充電期間中のR2の両端の電圧がすでにわかっています。ここで、vc = vE = Vpの場合、UJTデバイスはスイッチオン状態になり、コンデンサは時定数に応じた速度でRB1とR2を介して放電します。

τ=(RB1 + R2)C

次の式は、次の場合の放電時間を計算するために使用できます。

vc = vE

あなた≅ Vpe -t /(RB1 + R2)C

この式は、エミッタ電流が増加するにつれて値が減少するRB1と、C全体の放電率にも影響を与えるR1やVなどの回路の他の側面のために、少し複雑になっています。

それにもかかわらず、上記の図#8(b)の等価回路を参照すると、通常、R1とRB2の値は、コンデンサC周辺の構成のテブナンネットワークがR1の影響をわずかに受ける可能性があります。 RB2抵抗。電圧Vはかなり大きいように見えますが、以下の縮小等価図に示すように、テブナン電圧を補助する抵抗分割器は一般に見落とされて排除される可能性があります。

したがって、上記の簡略化されたバージョンは、VR2がピークにあるときのコンデンサCの放電位相について次の式を得るのに役立ちます。

VR2≅R2(Vp-0.7)/ R2 + RB1

より多くのアプリケーション回路については、 この記事を参照してください

前:ミニトランシーバー回路 次へ:PIR盗難警報回路