VLSIという用語は「超大規模集積回路」の略で、何千もの集積回路(IC)を組み合わせて設計することを含みます。 トランジスタ 論理的にシングルチップに 異なる論理回路 。これらのICは、従来のICを使用した回路と比較して、最終的に占有回路スペースを削減します。計算能力とスペース使用率は、VLSI設計の主な課題です。 VLSIプロジェクトを実施することで、研究者だけでなく学生にも挑戦的で明るいキャリアが開かれます。 VLSIの新しいトレンド分野のいくつかは フィールド・プログラマブル・ゲート・アレイ アプリケーション(FPGA)、ASICデザイン、およびSOC。この分野のプロジェクトを真剣に探している学生のために、いくつかのVLSIプロジェクトのリストを以下に示します。この記事では、FPGA、ザイリンクス、IEEE、Mini、Matlabなどに基づくVLSIプロジェクトの概要について説明します。これらのプロジェクトは、工学部の学生、M.techの学生にとって非常に役立ちます。

工学部の学生のためのVLSIプロジェクト

電子工学の学生向けの要約を含むVLSIプロジェクトについて以下で説明します。

VLSIプロジェクト

1)。離散ウェーブレットの変換-3Dリフティングに基づく

このプロジェクトは、データを失うことなく画像のコーディングを使用することにより、高精度の画像を提供するのに役立ちます。これを実現するために、このプロセスでは、3D離散ウェーブレットVLSIアーキテクチャの変換に応じてリフティングフィルターを実装します。

2)。高速ハードウェアを介して効率的に4ビットのSFQ乗算器を設計する

このプロジェクトは主に、4ビットSFQベースの修正ブースエンコーダー(MBE)を実装するために使用されます 乗数 。この乗算器は、従来のブースエンコーダと比較して優れたパフォーマンスを提供します。このプロジェクトは、主にクリティカル遅延のアプリケーションで使用されます。

3)。効率的な領域を備えたスマートカードで使用される暗号化プロセッサ

このプロジェクトは、で使用される秘密鍵と公開鍵の両方でサポートされる3つの暗号化アルゴリズムを実装するために使用されます スマートカード 非常に安全なユーザー検証とデータを提供するためのアプリケーション コミュニケーション 。

4)。スプリアスパワー抑制方式の高速または低電力乗算器

この提案されたシステムは、最後の計算結果に影響を与えない不必要なデータ送信を回避するために、算術ユニットの役に立たない誤った信号を除外します。このシステムは、乗算器にSPST方式を使用して、低電力で高速のデータ伝送を実現します。

5)。ロスレスデータアルゴリズムの圧縮と解凍

このプロジェクトは主に、PDLZW(Parallel Dictionary LZW)アルゴリズム機能と、ロスレスデータ圧縮とロスレス解凍の両方のアプリケーションに使用される適応形ハフマン型アルゴリズムに応じた2ステージハードウェアアーキテクチャで実装されます。

6)。エネルギー効率の高いWSNのための低複雑度のターボデコーダーのアーキテクチャ

提案されたシステムは、LUT-Log-BCJRの分解アルゴリズムから基本的なACS(Add Compare Select)操作を通じて、WSNのデータ送信全体の総エネルギー消費量を削減するために使用されます。

7)。画像のインパルスノイズを効率的に除去するためのVLSIアーキテクチャ

この提案されたシステムは、主に、インパルスノイズによって破損する可能性を回避するために視覚的に画質を向上させ、エッジ保存フィルターの助けを借りて効率的なVLSIアーキテクチャを実装するために使用されました。

8)。マルチメディアの圧縮に使用されるインメモリプロセッサのアーキテクチャ

この提案されたシステムは、 プロセッサー マルチメディアアプリケーション、すなわち画像圧縮、巨大な単一命令、複数のデータ概念および命令ワードを適用することによるビデオをサポートするためのメモリ内。

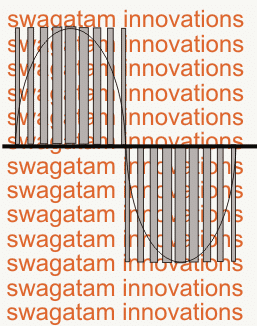

9)。低電力のワイヤレスOFDMシステム用のシンボルレートを使用したタイミング同期技術

この提案されたシステムは、主に無線OFDM(直交周波数分割)の動作を改善するために使用されます 多重化 )クロックの助けを借りてベースバンド全体の電力を減らすことによるシステム 発生器 位相調整可能で動的なサンプルタイミングコントローラーを備えています。

10)。 SPST加算器とVerilogを使用したアキュムレータベースの低電力および高速乗算器の実装

このプロジェクトは、MBE(変更されたブースエンコーダー)の電力の誤った抑制方法を受け入れることにより、低電力および高速MAC(乗算器およびアキュムレーター)を設計するために使用されます。この設計を使用することにより、スイッチング全体の消費電力を回避できます。

11)。 RFID技術との衝突防止を可能にすることによるロボットプロセッサの設計と実装

提案されたシステムは、主に、マルチロボットの環境でのロボットの物理的な衝突を回避するために、衝突防止機能を備えたロボットプロセッサを実装するために使用されます。このアルゴリズムは、主にVHDLおよびRFIDテクノロジーを使用して実装されます。

12)。断熱法を用いた電力効率の良い論理回路の設計

このシステムは、従来のCMOS設計と比較して、断熱法を使用して効率的に論理回路設計を示しています。 NANDおよびNORゲート 。断熱法を使用することにより、ネットワーク内の電力損失を削減し、負荷コンデンサ内に蓄積されたエネルギーを再利用することができます。

3)。システムの計算速度を向上させるための暗号化システム

このプロジェクトの主な目的は、FPGAを使用してAESのアルゴリズムを実装することにより、データ転送のセキュリティを強化してコンピューティングの速度を向上させることです。したがって、このシミュレーションと数学的設計は、VHDLコードを使用して実行できます。

14)。 AHMまたは高度な高性能バスのIPブロック

このプロジェクトは、主にAdvancedのアーキテクチャを設計するために使用されます マイクロコントローラー AHBN(Advanced High-Performance Bus)を使用したバス(AMB)。このプロジェクトは、master&saveなどのブロックを実装することでVHDLコードを使用して設計できます。

15)。マルチチャネルを備えたDSMベースのマルチモードRFトランシーバー

このシステムは、主にマルチモード送信機および受信機アーキテクチャとデルタシグマ変調器を備えたRFマルチチャネルの設計に使用されます。この提案されたシステムは、VHDL言語を使用して2つのアーキテクチャを実装します。

16)。非同期転送モードを使用したノックアウトスイッチのコンセントレータ

このプロジェクトを使用することにより、非同期転送に基づくノックアウトスイッチをVHSやVHDLなどのツールを使用して設計できます。このノックアウトスイッチは、仮想回線パケットのネットワークやデータグラムのアプリケーションで使用できます。

17)。非同期回路の動作合成

このプロジェクトは主に、非同期回路に使用される動作合成手法を提供するために使用されます。バルサと非同期実装のような両方のテンプレートは、デザイン内の主要な要素です。

18)。 AHBの準拠メモリコントローラーを使用したAMBA設計

このプロジェクトは、SRAMやROMなどのメインメモリを使用してシステムメモリを制御するために、AMBA(アドバンストマイクロコントローラバスアーキテクチャ)に依存するMC(メモリコントローラ)を設計するために使用されます。

19)。キャリーツリー加算器の実装

VLSI設計に基づくキャリーツリー加算器は、通常のバイナリ加算器とは対照的に、最高のパフォーマンスの加算器と呼ばれます。このプロジェクトによって実装される加算器は、スパニングツリー、kogge-stone、およびスパースkogge-stoneです。

20)。 CORDICデザインベースの固定角度回転

この提案されたシステムの主な概念は、固定角度を使用してベクトルを回転させることです。これらの角度は、ゲーム、ロボット工学、 画像処理 このプロジェクトを使用することにより、CORDIC(座標回転デジタルコンピュータ)の設計により、特定の角度を使用してベクトル回転を実現できます。

21)。ルックアップテーブルの分散演算を使用したFIRフィルターの設計

この提案されたシステムは主に FIRフィルター 乗数の代わりに3次元ルックアップテーブルの分散演算を使用して設計することによるパフォーマンス。したがって、このデザインは、FPGAやザイリンクスなどのソフトウェアを使用して実装できます。

22)。高速&低電力条件付きプッシュプルパルスラッチ

このプロジェクトは、新しいトポロジーを使用して、主にVLSIシステムに使用されるエネルギー効率の高い高性能パルスラッチを実行するために使用されます。このトポロジは主に、条件付きパルスジェネレータを介して2つの分割レーンを使用して駆動される最終段階のプッシュプルに依存しているためです。

23)。 SPIHTの算術コーダーVLSIアーキテクチャ

この提案されたシステムは、FPGAに依存する高速アーキテクチャを使用して、階層ツリーでのセットパーティショニング(SPIHT)画像圧縮における算術符号化の方法のスループットを向上させます。

24)。 FPGAに基づくECG信号のノイズ抑制

このプロジェクトは、それぞれ91と7のサンプルポイントサイズを持つ2つのメディアンフィルターを介してECG信号内のノイズを封じ込めるために使用されます。したがって、このプロセスは、 FPGAデザイン VHDLコードに基づいています。

25)。低コストのVLSIベースの高性能画像スケーリングプロセッサ

このプロジェクトは、メモリが少なく高性能なVLSIに基づく画像スケーリングプロセッサのアルゴリズムを実装するために使用されます。提案されたシステム設計には、主に、コストを削減するためのフィルター、再構成可能な動的手法、およびハードウェア共有の組み合わせが含まれています。

26)。シストリックアレイアーキテクチャの設計と実装を効率的に

このプロジェクトの主なコンセプトは、シストリックアレイ乗算器に使用されるハードウェアモデルを設計することです。この配列は、主にVHDLプラットフォームを使用してバイナリ乗算を実行するために使用できます。提案されたシステム設計は、FPGAおよびIsimソフトウェアを使用して実装できます。

27)。 VHDLコードを使用したQPSKの設計と合成

QPSK は主要な変調方式の1つです。この方法は、衛星ラジオのアプリケーションで使用されます。この変調技術は、可逆論理ゲートを介して実装できます。 QPSK技術の設計は、VHDLコードを使用して行うことができます。

28)。高速でのDDRSDRAMコントローラーの設計と実装

提案されたシステムは、組み込みシステムの回路とDDRSDRAMの間でこのデータを同期するために高速に応じてバーストデータを転送するためのDDRSDRAMコントローラーを設計するために使用されます。 VHDL言語を使用することにより、コードを開発できます。

29)。 32ビットRISCプロセッサの設計と実装

このプロジェクトの主なコンセプトは、32ビットを実装することです RISC(縮小命令セットコンピュータ) XILINKVIRTEX4のようなツールの助けを借りて。このプロジェクトでは、5フェーズパイプライン方式を使用してすべての命令を単一のCLKサイクルで実行できる場合は常に、16個の命令セットが設計されています。

30)。 AHBとOCP間のバスブリッジの実装

提案されたシステムは、2つのプロトコル、つまり共通プロトコルと標準プロトコルの間のバスブリッジを設計するために使用されます。 AHB(Advanced High-performance Bus)やOCP(Open Core Protocol)などの通信プロトコルは非常に人気があり、 SoC(システムオンチップ) 。

工学部の学生のためのVLSIプロジェクトのアイデア

FPGA、MatLab、IEEE、および工学部の学生向けのミニプロジェクトに基づくVLSIプロジェクトのリストを以下に示します。

M.Tech学生のためのVLSIプロジェクト

M. Tech Studentに基づくVLSIプロジェクトのリストには、次のものが含まれます。

- 航空宇宙アプリケーションで使用されるエリア効率が高く信頼性の高いRHBDベースのI0Tメモリセル設計

- CLKおよびデータ回復回路に使用されるマルチレベルハーフレートの位相検出器

- 正確なアプリケーションに使用される低電力および高速のコンパレータ

- 高性能で統合されたマルチプレクサを備えたゲート電圧レベルトランスレータ

- 高性能のCNTFETベースの3進加算器

- 低電力のマグニチュードコンパレータ設計

- 遅延解析用の電流モードを備えたしきい値論理ゲートの設計

- 低電力で高性能な混合論理ラインデコーダーの設計

- スリープコンベンションロジックのテスト容易性設計

- 高速で電力効率の高いデュアルサプライアプリケーション用の電圧レベルシフター

- 低電力および低電圧のダブルテールコンパレータの設計と分析

- 信号フィードスルー方式を使用した低電力でのパルストリガーに基づくフリップフロップ設計

- ランタイム再構成可能FETに基づく効率的な回路設計

- 低電力のマグニチュードコンパレータ設計

- 電流モードしきい値を使用した論理ゲート設計の遅延分析

ザ・ FPGAベースのVLSIプロジェクト 工学部の学生と CMOSVLSI設計ミニプロジェクト 以下にリストされています。

- SRAMに基づくFPGAのSEU硬化回路の設計と特性評価

- FPGAで使用されるコンパクトなメモリスタベースのCMOSハイブリッドLUTデザインと潜在的なアプリケーション

- 距離測定用のFPGAの超音波センサーベースの実装

- Spartan6FPGAを使用したブース乗算器用FPGAの実装

- Spartan3FPGAを使用したリフティングに基づく離散ウェーブレット変換

- FPGAを使用したロボット工学のARMコントローラー

- マルチチャネルを備えたFPGAベースのUART

- FPGAを使用したECG信号ノイズの抑制

- UTMIベースのFPGA実装とUSB2.0プロトコルレイヤー

- Spartan3FPGAを使用したメディアンフィルターの実装

- FPGAのAESアルゴリズムベースの実装

- Spartan3anでFPGAを実装するためのPICに基づくセキュリティアラートシステム

- リモートセンシングシステム用のコントローラーを設計するためのFPGA実装

- 線形および形態学的な画像フィルタリングを使用したFPGAの画像処理キット

- Spartan3FPGAベースの医療フュージョンイメージの実装

のリスト VHDLコードを使用したVLSIミニプロジェクト 以下が含まれます。

- VLSIを使用した高速コンパレータ

- VLSIを使用した浮動小数点の乗算器

- バイナリからグレーへのVLSIベースの変換

- デジタルフィルター

- VLSIに基づくCLKゲーティング

- ヴェーダ乗数

- VLSIを使用したCMOSFF

- VLSIを使用した並列プロセッサのアーキテクチャ

- VLSIベースの全加算器

- VLSIに基づくDRAM /ダイナミックランダムアクセスメモリの設計

- VLSIに基づくSRAMレイアウト

- VLSIベースのデジタルシグナルプロセッサ

- VLSIベースのマルチプレクサ

- VLSIに基づくMACユニットの設計

- VLSIベースの微分器

- VLSIベースのFFTまたは高速フーリエ変換

- VLSIに基づく離散コサイン変換のアーキテクチャ

- VLSI19を使用した16ビット乗算器の設計

- FIFOバッファのVLSIベースの設計

- VLSIベースの高速アクセラレータ

MATLABとザイリンクスを使用したVLSIプロジェクト

MATLABに基づくVLSIプロジェクトとザイリンクスを使用したVLSIプロジェクトのリストには、次のものが含まれます。

- MATLABを使用したCDMAモデムの設計と分析

- FPGAおよびMATLABベースの分析でVHDLを使用したFIRフィルターの設計

- ModelSim&MatlabまたはSimulinkベースの自動車工学システムのシミュレーション

- Ripple Carry&CarrySkipなどのザイリンクスベースの加算器

- 32ビット浮動小数点に基づく算術演算装置

- 浮動小数点ベースのALU

- 32ビットベースのRISCプロセッサ

- 直交コードの畳み込み機能

- ザイリンクスおよびVerilogベースの自動販売機

- 256ビットのザイリンクスベースの並列プレフィックス加算器

- ザイリンクスを使用した相互認証のプロトコル

- ザイリンクスを使用したロジックテストのシングルサイクルのアクセス構造

- ザイリンクスを使用したUTMIおよびプロトコルレイヤーベースのUSB2.0

- ザイリンクスFPGAを使用したデータの圧縮と解凍の構成

- ザイリンクス4000ベースのBISTおよびSpartanシリーズベースのFPGA

- MATLABとVLSIに基づくIIRフィルター

- MATLABを使用したFIRフィルター

IEEEプロジェクト

ザ・ IEEEVLSIプロジェクトのリスト 以下にリストされています。

- Bluetoothを使用したVLSIベースのワイヤレスホームオートメーションシステム

- VLSIの効率的なアーキテクチャを使用した画像内のインパルスノイズの除去

- マルチメディア圧縮用のプロセッサインメモリのアーキテクチャ

- クラウドとIoTを使用した温度システムの監視

- IFFTおよびFFTを使用したOFDMシステムの実装

- Verilogによるハミングコードの設計と実装

- ガボールフィルターを使用したVHDLベースの指紋認識

- 近似アプローチに応じたROMによる算術関数の再マッピング

- 低電力アプリケーションにおけるパリティチェックコードデコーダの高効率および低密度性能の分析

- パイプライン基数-2kのフィードフォワードを備えたFFTアーキテクチャ

- 高性能のCMOS技術を使用したVLSIアプリケーション用のフリップフロップ設計

- 分散演算によるルックアップテーブルを使用したFIRフィルターの設計

- VLSIベースの低コストで強化された画像スケーリングプロセッサ

- 3GPPLTEを使用したAdvanceTurboエンコーダーおよびデコーダーのASIC実装および設計

- 低電力および高速条件付きプッシュプルパルスラッチ

- 低電力スキャンテストでの強化されたスキャン

- SPIHT用の算術コーダーVLSIアーキテクチャ

- UART用のVHDLの実装

- 低ドロップアウトのVLSIベースの電圧レギュレータ

- コンパレータ方式が強化されたフラッシュADC設計

- 複合定遅延ロジックスタイルを使用した低電力乗算器の設計

- 高性能&低電力のダブルテールコンパレータ

- 書き込みバッファと仮想メモリに依存する高性能のフラッシュストレージシステム

- スリーピースタックアプローチに基づく低電力FF

- HDLに実装された低電力BISTのLFSR電力最適化

- VerilogHDLを使用した自動販売機の設計と実装

- LP-LSFRによる3ウェイトパターンの生成に基づくアキュムレータ設計

- 高速で複雑度の低いリードソロモンデコーダー

- より高速なDadda乗数設計手法

- FMラジオのデジタル復調ベースの受信機

- BISTスキームを使用したテストパターンの生成

- 高速パイプラインによるVLSIアーキテクチャの実装

- バス機能を使用したオンチップバスOCPプロトコル設計

- 高周波フェーズロックループに使用される位相周波数検出器とチャージポンプの設計

- VHDLを使用したキャッシュメモリとキャッシュコントローラの設計

- ASTRANベースの低電力3-2および4-2加算器コンプレッサーの実装

- オンチップ設計を使用したプリペイド電気料金請求システム

- ロジックセルとその検出力分析を使用したオーバーラップ実装

- キャリールックアヘッド加算器 VHDLを使用したさまざまなビットパフォーマンス分析

- Wi-FiMACを使用したデータリンク層の設計 プロトコル

- モジュラー演算を使用した相互認証プロトコル用のFPGAの実装

- FPGAと可変デューティサイクルを使用したPWM信号生成

リアルタイムプロジェクト

のリスト VLSIリアルタイムプロジェクト 主に、VHDLコードを使用したVLSIミニプロジェクトとECEエンジニアリングの学生向けのVLSIソフトウェアプロジェクトが含まれます。

- TSVを使用した異種3DDRAMアーキテクチャへのSRAM行キャッシュの実用的な統合

- クラスタベースのフィールドプログラマブルゲートアレイの遅延障害を診断するための組み込みセルフテスト技術

- 複雑な乗数のASIC設計

- インパルスノイズを効率的に除去するための低コストVLSI実装

- FPGAベース 空間ベクトルPWM 三相誘導電動機駆動用制御IC

- OFDMベースのWLAN用の自動相関器とCORDICアルゴリズムのVLSI実装

- 高解像度衛星画像を使用した自動道路抽出

- 病気の検出にガボールフィルターを使用した画像セグメンテーションのためのVHDLデザイン

- エネルギー効率の高い無線センサーネットワークのための低複雑度ターボデコーダーアーキテクチャ

- FPGA実装を使用した直交コード畳み込み機能の改善

- 浮動小数点ALUの設計と実装

- 固定回転角のCORDICデザイン

- FPGAチップにNANDフラッシュコントローラーを実装するための製品リードソロモンコード

- 負の静電容量回路を使用した統計的SRAM読み取りアクセス歩留まりの改善

- モバイルシステムでのMIMOネットワークインターフェイスの電力管理

- データ暗号化のためのデータ暗号化標準の設計

- 低電力で面積効率の高いキャリーセレクト加算器

- VHDLコードを使用したUARTの合成と実装

- 融合浮動小数点加算-減算ユニットのアーキテクチャの改善

- SDR用のRF出力を備えたデルタシグマ変調を採用したFPGAベースの1ビットオールデジタルトランスミッタ

- 高エラーレート送信のためのBCHデコーダーでのチェーン検索の使用の最適化

- VerilogHDLおよびFPGAを使用したDS-CDMA送信機のデジタル設計

- 効率的なシストリックアレイアーキテクチャの設計と実装

- VLSIベースのロボットダイナミクス学習アルゴリズム

- スプリアスパワー抑制技術を使用した多用途のマルチメディア機能ユニット設計

- AHBとOCP間のバス橋の設計

- 非同期回路の動作合成

- FPGAベースの修正ビタビデコーダーの速度最適化

- I2Cインターフェースの実装

- 高度なスプリアスパワー抑制技術を使用した高速/低電力乗算器

- アクティブリーク低減とゲート酸化信頼性のためのパワーゲーティング回路の仮想供給電圧のクランプ

- ソフトウェア無線用のFPGAベースの電力効率の高いチャネライザー

- 画像のセキュリティと認証のためのデジタルカメラのVLSIアーキテクチャとFPGAプロトタイピング

- 室内ロボットの動作改善

- マルチプロセッサシステムオンチップ用のオンチップ順列ネットワークの設計と実装

- 低電力無線OFDMシステムのシンボルレートタイミング同期方式

- VHDL / VLSIを使用したDMAコントローラー(ダイレクトメモリアクセス)

- MIMI-OFDM受信機用のCORDICベースのアーキテクチャを使用した再構成可能なFFT

- マルチメディア/ DSPアプリケーションのためのスプリアス電力抑制技術

- 電子透かしにおけるBCHコードの効率

- デュアルデータレートSD-RAMコントローラー

- VerilogHDLを使用した指紋認識用のガボールフィルターの実装

- 1回の挿入速度で冗長性を向上させるためのAwareStandard CellLibraryによる実用的なナノメートルスケールの冗長性の設計

- ロスレスデータ圧縮および解凍アルゴリズムとそのハードウェアアーキテクチャ

- マルチビットソフトエラーを修正するためのフレームワーク

- ビタビベースの効率的なテストデータ圧縮

- OFDM用のFFT / IFFTブロックの実装

- VLSIプログレッシブコーディングによるウェーブレットベースの画像圧縮

- Jpeg用の完全にパイプライン化された乗算器レス2dDCT / IDCTアーキテクチャのVLSI実装

- 同期シーケンシャル回路のFPGAベースのフォールトエミュレーション

したがって、これはすべて、最終年度のプロジェクトトピックを選択するのに役立つ工学修士課程の学生向けのVLSIプロジェクトのリストに関するものです。このリストを読みながら貴重な時間を過ごした後、VLSIプロジェクトのリストから選択したプロジェクトのトピックを選択するというかなり良いアイデアが得られたと思います。そして、リスト。これらのプロジェクトの詳細とヘルプについては、以下のコメントセクションにご連絡ください。ここにあなたへの質問があります、VHDLとは何ですか?

フォトクレジット

- VLSIプロジェクト セットテック